- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375146 > A62S8308 (AMIC Technology Corporation) 256K X 8 BIT LOW VOLTAGE CMOS SRAM PDF資料下載

參數(shù)資料

| 型號(hào): | A62S8308 |

| 廠商: | AMIC Technology Corporation |

| 英文描述: | 256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| 中文描述: | 256K × 8位低電壓CMOS的SRAM |

| 文件頁(yè)數(shù): | 11/17頁(yè) |

| 文件大小: | 278K |

| 代理商: | A62S8308 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)

A62S8308 Series

PRELIMINARY

(March, 2001, Version 0.2)

10

AMIC Technology, Inc.

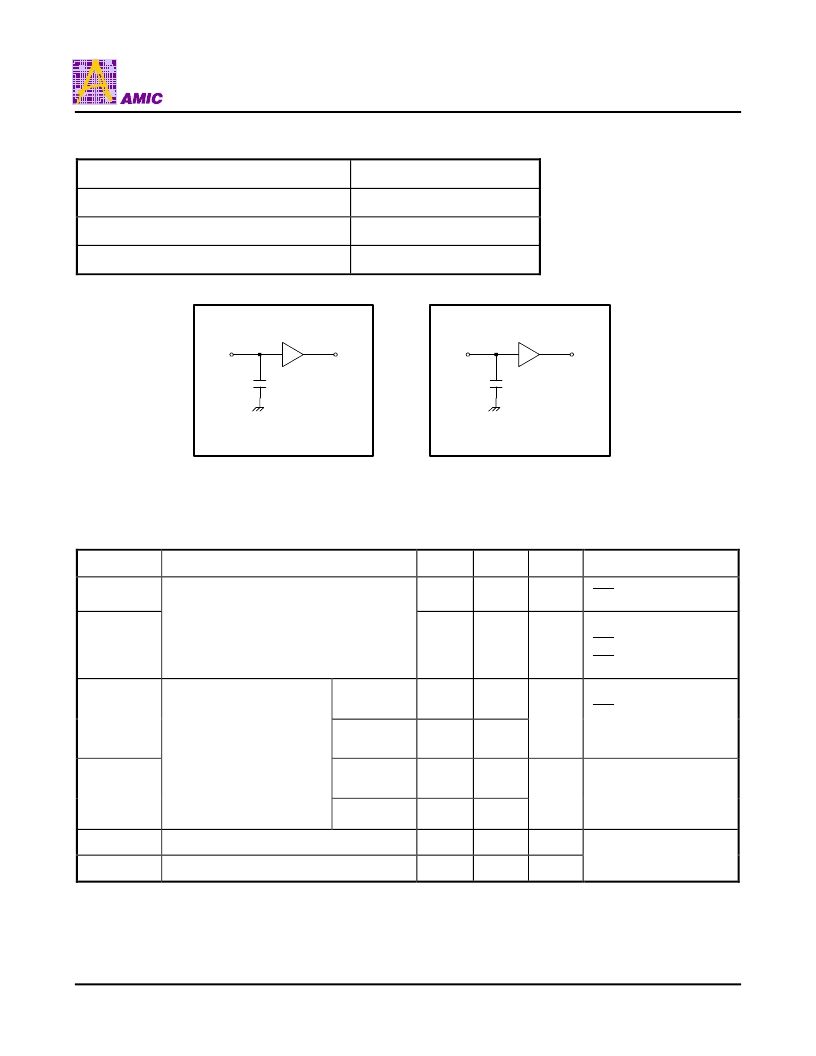

AC Test Conditions

Input Pulse Levels

0V to 3.0V

Input Rise and Fall Time

5 ns

Input and Output Timing Reference Levels

1.5V

Output Load

See Figures 1 and 2

30pF

* Including scope and jig.

* Including scope and jig.

C

L

TTL

5pF

C

L

TTL

Data Retention Characteristics

(T

A

= 0

°

C to + 70

°

C or -25

°

C to 85

°

C)

Figure 1. Output Load

Figure 2. Output Load for t

CLZ1

,

t

CLZ2

, t

OHZ

, t

OLZ

, t

CHZ1

,

t

CHZ2

, t

WHZ

, and t

OW

Symbol

Parameter

Min.

Max.

Unit

Conditions

V

DR1

2.0

3.6

V

CE1

≥

VCC - 0.2V

V

DR2

VCC for Data Retention

2.0

3.6

V

CE2

≤

0.2V

CE1

≥

VCC - 0.2V or

CE1

≤

0.2V

I

CCDR1

S-Version

-

5*

μ

A

VCC = 2.0V

CE1

≥

VCC - 0.2V

CE2

≥

VCC - 0.2V

V

IN

≥

0V

Data Retention Current

SI-Version

-

10**

I

CCDR2

S-Version

-

5*

μ

A

VCC = 2.0V

CE2

≤

0.2V

V

IN

≥

0V

SI-Version

-

10**

t

CDR

Chip Disable to Data Retention Time

0

-

ns

t

R

Operation Recovery Time

t

RC

-

ns

See Retention Waveform

* A62S8308-55S/70S

** A62S8308-55SI/70SI

I

CCDR

: Max. 1

μ

A at T

A

= 0

°

C + 40

°

C

I

CCDR

: Max. 1

μ

A at T

A

= 0

°

C + 40

°

C

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| A62S8308G-70SI | 256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308M-55S | 256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308M-55SI | 256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308M-70S | 256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308M-70SI | 256K X 8 BIT LOW VOLTAGE CMOS SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| A62S8308G-55S | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308G-55SI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308G-70S | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308G-70SI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:256K X 8 BIT LOW VOLTAGE CMOS SRAM |

| A62S8308M-55S | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:256K X 8 BIT LOW VOLTAGE CMOS SRAM |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。