- 您現(xiàn)在的位置:買賣IC網 > PDF目錄375144 > A625308AM-70S (AMIC Technology Corporation) 32K X 8 BIT CMOS SRAM PDF資料下載

參數(shù)資料

| 型號: | A625308AM-70S |

| 廠商: | AMIC Technology Corporation |

| 英文描述: | 32K X 8 BIT CMOS SRAM |

| 中文描述: | 32K的× 8位CMOS的SRAM |

| 文件頁數(shù): | 9/14頁 |

| 文件大小: | 141K |

| 代理商: | A625308AM-70S |

A625308A Series

PRELIMINARY (July, 2002, Version 0.2)

8

AMIC Technology, Inc.

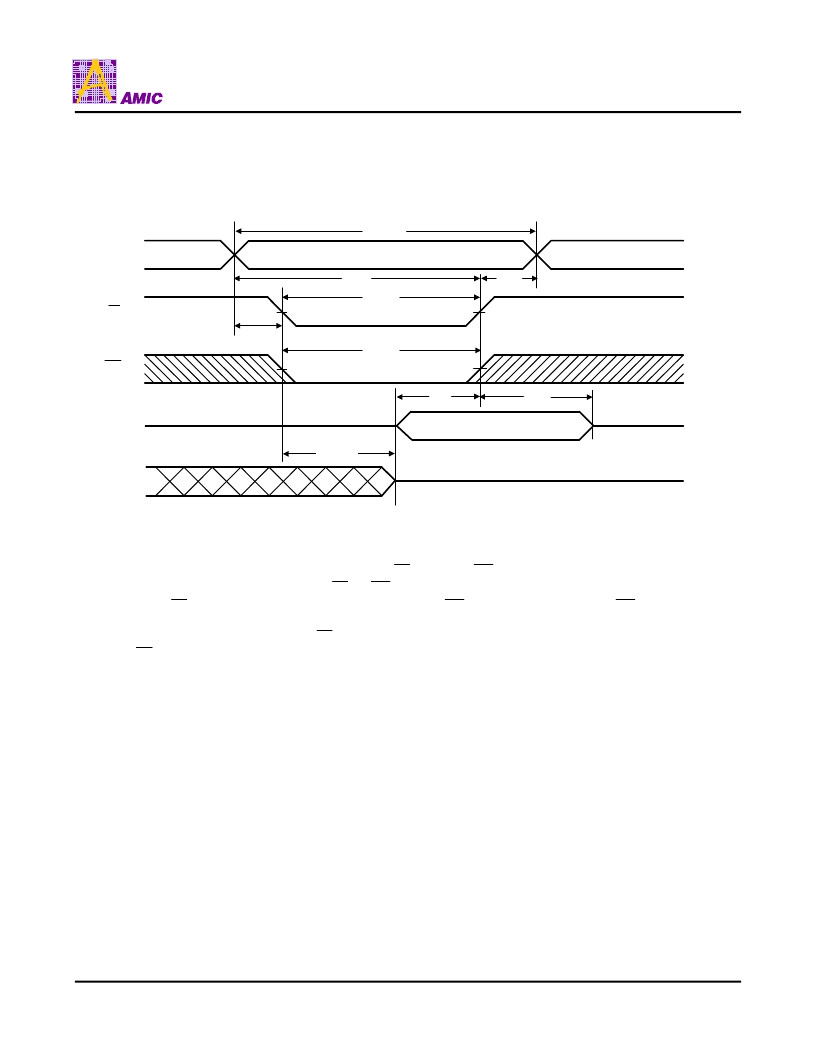

Timing Waveforms (continued)

Write Cycle 2

(6)

(Chip Enable Controlled)

t

WC

Address

CE

D

IN

t

DH

t

DW

(4)

t

CW5

t

AW

t

WR3

WE

D

OUT

t

WHZ7

t

WP2

t

AS1

Notes: 1. t

AS

is measured from the address valid to the beginning of Write.

2. A Write occurs during the overlap (t

WP

) of a low CE and a low WE .

3. t

WR

is measured form the earliest of CE or WE going high to the end of the Write cycle.

4. If the CE low transition occurs simultaneously with the WE low transition or after the WE transition, outputs

remain in a high impedance state.

5. t

CW

is measured from the later of CE going low to the end of Write.

6. OE level is high or low.

7. Transition is measured

±

500mV from steady. This parameter is sampled and not 100% tested.

相關PDF資料 |

PDF描述 |

|---|---|

| A625308AM-70SI | 32K X 8 BIT CMOS SRAM |

| A625308AM-70SU | 32K X 8 BIT CMOS SRAM |

| A625308AV-70S | 32K X 8 BIT CMOS SRAM |

| A625308AV-70SI | 32K X 8 BIT CMOS SRAM |

| A625308AV-70SU | 32K X 8 BIT CMOS SRAM |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| A625308AM-70SI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:32K X 8 BIT CMOS SRAM |

| A625308AM-70SU | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:32K X 8 BIT CMOS SRAM |

| A625308ASERIES | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:32K X 8 BIT CMOS SRAM |

| A625308AV-70S | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:32K X 8 BIT CMOS SRAM |

| A625308AV-70SI | 制造商:AMICC 制造商全稱:AMIC Technology 功能描述:32K X 8 BIT CMOS SRAM |

發(fā)布緊急采購,3分鐘左右您將得到回復。