- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄189002 > NAND08GR4B2AZC6E (NUMONYX) 512M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 PDF資料下載

參數(shù)資料

| 型號(hào): | NAND08GR4B2AZC6E |

| 廠商: | NUMONYX |

| 元件分類(lèi): | PROM |

| 英文描述: | 512M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| 封裝: | 9.50 X 12 MM, 1.40 MM HEIGHT, 0.80 MM PITCH, ROHS COMPLIANT, LFBGA-63 |

| 文件頁(yè)數(shù): | 44/59頁(yè) |

| 文件大小: | 998K |

| 代理商: | NAND08GR4B2AZC6E |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)當(dāng)前第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)

49/59

NAND512-B, NAND01G-B, NAND02G-B, NAND04G-B, NAND08G-B

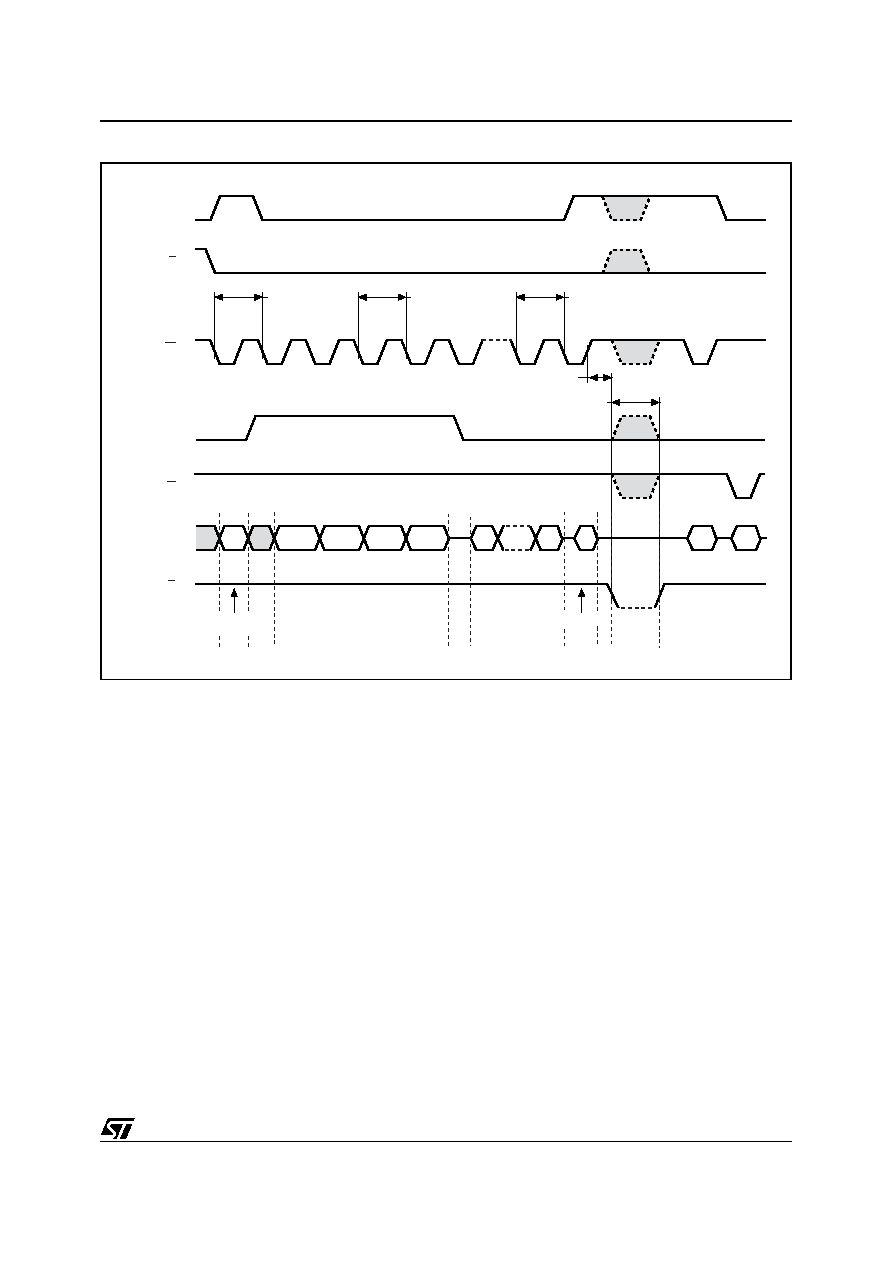

Figure 32. Page Program AC Waveform

Note: A fifth address cycle is required for 2Gb, 4Gb and 8Gb devices.

CL

E

W

AL

R

I/O

RB

SR0

ai08668

N

Last

10h

70h

80h

Page Program

Setup Code

Confirm

Code

Read Status Register

tWLWL

tWHBL

tBLBH2

Page

Program

Address Input

Data Input

Add.N

cycle 1

Add.N

cycle 4

Add.N

cycle 3

Add.N

cycle 2

(Write Cycle time)

(Program Busy time)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| NAND512R3B3CZA6 | 64M X 8 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND01GR4B3CZA1E | 64M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND01GR4B3CZA6E | 64M X 16 FLASH 1.8V PROM, 35 ns, PBGA63 |

| NAND01GW4B3BN6T | 64M X 16 FLASH 3V PROM, 35 ns, PDSO48 |

| NAND01GW4B3CZA1E | 64M X 16 FLASH 3V PROM, 35 ns, PBGA63 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| NAND08GW3B2AN6E | 功能描述:閃存 4 GBit 2112 Byte 1056 WP 1.8v/3v RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲(chǔ)類(lèi)型:Flash 存儲(chǔ)容量:2 MB 結(jié)構(gòu):256 K x 8 定時(shí)類(lèi)型: 接口類(lèi)型:SPI 訪問(wèn)時(shí)間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| NAND08GW3B2AN6F | 功能描述:閃存 4 GB 2112B 1056 Word Pg 1.8V/3V RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲(chǔ)類(lèi)型:Flash 存儲(chǔ)容量:2 MB 結(jié)構(gòu):256 K x 8 定時(shí)類(lèi)型: 接口類(lèi)型:SPI 訪問(wèn)時(shí)間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| NAND08GW3B2BN6E | 制造商:Micron Technology Inc 功能描述:NAND & S.MEDIA FLASH - Trays |

| NAND08GW3B2CN6E | 功能描述:閃存 NAND & S.MEDIA FLASH RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲(chǔ)類(lèi)型:Flash 存儲(chǔ)容量:2 MB 結(jié)構(gòu):256 K x 8 定時(shí)類(lèi)型: 接口類(lèi)型:SPI 訪問(wèn)時(shí)間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

| NAND08GW3B2CN6F | 功能描述:閃存 NAND & S.MEDIA FLASH RoHS:否 制造商:ON Semiconductor 數(shù)據(jù)總線寬度:1 bit 存儲(chǔ)類(lèi)型:Flash 存儲(chǔ)容量:2 MB 結(jié)構(gòu):256 K x 8 定時(shí)類(lèi)型: 接口類(lèi)型:SPI 訪問(wèn)時(shí)間: 電源電壓-最大:3.6 V 電源電壓-最小:2.3 V 最大工作電流:15 mA 工作溫度:- 40 C to + 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體: 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。