- 鎮ㄧ従(xi脿n)鍦ㄧ殑浣嶇疆锛�璨�(m菐i)璩�(m脿i)IC缍�(w菐ng) > PDF鐩寗4494 > A3P600L-FGG484 (Microsemi SoC)IC FPGA 1KB FLASH 600K 484-FBGA PDF璩囨枡涓嬭級

鍙冩暩(sh霉)璩囨枡

| 鍨嬭櫉(h脿o)锛� | A3P600L-FGG484 |

| 寤犲晢锛� | Microsemi SoC |

| 鏂囦欢闋�(y猫)鏁�(sh霉)锛� | 62/242闋�(y猫) |

| 鏂囦欢澶у皬锛� | 0K |

| 鎻忚堪锛� | IC FPGA 1KB FLASH 600K 484-FBGA |

| 妯�(bi膩o)婧�(zh菙n)鍖呰锛� | 40 |

| 绯诲垪锛� | ProASIC3L |

| RAM 浣嶇附瑷�(j矛)锛� | 110592 |

| 杓稿叆/杓稿嚭鏁�(sh霉)锛� | 235 |

| 闁€(m茅n)鏁�(sh霉)锛� | 600000 |

| 闆绘簮闆诲锛� | 1.14V ~ 1.575 V |

| 瀹夎椤�(l猫i)鍨嬶細 | 琛ㄩ潰璨艰 |

| 宸ヤ綔婧害锛� | 0°C ~ 70°C |

| 灏佽/澶栨锛� | 484-BGA |

| 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁濓細 | 484-FPBGA锛�23x23锛� |

绗�1闋�(y猫)绗�2闋�(y猫)绗�3闋�(y猫)绗�4闋�(y猫)绗�5闋�(y猫)绗�6闋�(y猫)绗�7闋�(y猫)绗�8闋�(y猫)绗�9闋�(y猫)绗�10闋�(y猫)绗�11闋�(y猫)绗�12闋�(y猫)绗�13闋�(y猫)绗�14闋�(y猫)绗�15闋�(y猫)绗�16闋�(y猫)绗�17闋�(y猫)绗�18闋�(y猫)绗�19闋�(y猫)绗�20闋�(y猫)绗�21闋�(y猫)绗�22闋�(y猫)绗�23闋�(y猫)绗�24闋�(y猫)绗�25闋�(y猫)绗�26闋�(y猫)绗�27闋�(y猫)绗�28闋�(y猫)绗�29闋�(y猫)绗�30闋�(y猫)绗�31闋�(y猫)绗�32闋�(y猫)绗�33闋�(y猫)绗�34闋�(y猫)绗�35闋�(y猫)绗�36闋�(y猫)绗�37闋�(y猫)绗�38闋�(y猫)绗�39闋�(y猫)绗�40闋�(y猫)绗�41闋�(y猫)绗�42闋�(y猫)绗�43闋�(y猫)绗�44闋�(y猫)绗�45闋�(y猫)绗�46闋�(y猫)绗�47闋�(y猫)绗�48闋�(y猫)绗�49闋�(y猫)绗�50闋�(y猫)绗�51闋�(y猫)绗�52闋�(y猫)绗�53闋�(y猫)绗�54闋�(y猫)绗�55闋�(y猫)绗�56闋�(y猫)绗�57闋�(y猫)绗�58闋�(y猫)绗�59闋�(y猫)绗�60闋�(y猫)绗�61闋�(y猫)鐣�(d膩ng)鍓嶇62闋�(y猫)绗�63闋�(y猫)绗�64闋�(y猫)绗�65闋�(y猫)绗�66闋�(y猫)绗�67闋�(y猫)绗�68闋�(y猫)绗�69闋�(y猫)绗�70闋�(y猫)绗�71闋�(y猫)绗�72闋�(y猫)绗�73闋�(y猫)绗�74闋�(y猫)绗�75闋�(y猫)绗�76闋�(y猫)绗�77闋�(y猫)绗�78闋�(y猫)绗�79闋�(y猫)绗�80闋�(y猫)绗�81闋�(y猫)绗�82闋�(y猫)绗�83闋�(y猫)绗�84闋�(y猫)绗�85闋�(y猫)绗�86闋�(y猫)绗�87闋�(y猫)绗�88闋�(y猫)绗�89闋�(y猫)绗�90闋�(y猫)绗�91闋�(y猫)绗�92闋�(y猫)绗�93闋�(y猫)绗�94闋�(y猫)绗�95闋�(y猫)绗�96闋�(y猫)绗�97闋�(y猫)绗�98闋�(y猫)绗�99闋�(y猫)绗�100闋�(y猫)绗�101闋�(y猫)绗�102闋�(y猫)绗�103闋�(y猫)绗�104闋�(y猫)绗�105闋�(y猫)绗�106闋�(y猫)绗�107闋�(y猫)绗�108闋�(y猫)绗�109闋�(y猫)绗�110闋�(y猫)绗�111闋�(y猫)绗�112闋�(y猫)绗�113闋�(y猫)绗�114闋�(y猫)绗�115闋�(y猫)绗�116闋�(y猫)绗�117闋�(y猫)绗�118闋�(y猫)绗�119闋�(y猫)绗�120闋�(y猫)绗�121闋�(y猫)绗�122闋�(y猫)绗�123闋�(y猫)绗�124闋�(y猫)绗�125闋�(y猫)绗�126闋�(y猫)绗�127闋�(y猫)绗�128闋�(y猫)绗�129闋�(y猫)绗�130闋�(y猫)绗�131闋�(y猫)绗�132闋�(y猫)绗�133闋�(y猫)绗�134闋�(y猫)绗�135闋�(y猫)绗�136闋�(y猫)绗�137闋�(y猫)绗�138闋�(y猫)绗�139闋�(y猫)绗�140闋�(y猫)绗�141闋�(y猫)绗�142闋�(y猫)绗�143闋�(y猫)绗�144闋�(y猫)绗�145闋�(y猫)绗�146闋�(y猫)绗�147闋�(y猫)绗�148闋�(y猫)绗�149闋�(y猫)绗�150闋�(y猫)绗�151闋�(y猫)绗�152闋�(y猫)绗�153闋�(y猫)绗�154闋�(y猫)绗�155闋�(y猫)绗�156闋�(y猫)绗�157闋�(y猫)绗�158闋�(y猫)绗�159闋�(y猫)绗�160闋�(y猫)绗�161闋�(y猫)绗�162闋�(y猫)绗�163闋�(y猫)绗�164闋�(y猫)绗�165闋�(y猫)绗�166闋�(y猫)绗�167闋�(y猫)绗�168闋�(y猫)绗�169闋�(y猫)绗�170闋�(y猫)绗�171闋�(y猫)绗�172闋�(y猫)绗�173闋�(y猫)绗�174闋�(y猫)绗�175闋�(y猫)绗�176闋�(y猫)绗�177闋�(y猫)绗�178闋�(y猫)绗�179闋�(y猫)绗�180闋�(y猫)绗�181闋�(y猫)绗�182闋�(y猫)绗�183闋�(y猫)绗�184闋�(y猫)绗�185闋�(y猫)绗�186闋�(y猫)绗�187闋�(y猫)绗�188闋�(y猫)绗�189闋�(y猫)绗�190闋�(y猫)绗�191闋�(y猫)绗�192闋�(y猫)绗�193闋�(y猫)绗�194闋�(y猫)绗�195闋�(y猫)绗�196闋�(y猫)绗�197闋�(y猫)绗�198闋�(y猫)绗�199闋�(y猫)绗�200闋�(y猫)绗�201闋�(y猫)绗�202闋�(y猫)绗�203闋�(y猫)绗�204闋�(y猫)绗�205闋�(y猫)绗�206闋�(y猫)绗�207闋�(y猫)绗�208闋�(y猫)绗�209闋�(y猫)绗�210闋�(y猫)绗�211闋�(y猫)绗�212闋�(y猫)绗�213闋�(y猫)绗�214闋�(y猫)绗�215闋�(y猫)绗�216闋�(y猫)绗�217闋�(y猫)绗�218闋�(y猫)绗�219闋�(y猫)绗�220闋�(y猫)绗�221闋�(y猫)绗�222闋�(y猫)绗�223闋�(y猫)绗�224闋�(y猫)绗�225闋�(y猫)绗�226闋�(y猫)绗�227闋�(y猫)绗�228闋�(y猫)绗�229闋�(y猫)绗�230闋�(y猫)绗�231闋�(y猫)绗�232闋�(y猫)绗�233闋�(y猫)绗�234闋�(y猫)绗�235闋�(y猫)绗�236闋�(y猫)绗�237闋�(y猫)绗�238闋�(y猫)绗�239闋�(y猫)绗�240闋�(y猫)绗�241闋�(y猫)绗�242闋�(y猫)

ProASIC3L DC and Switching Characteristics

2-138

Revision 13

Timing Characteristics

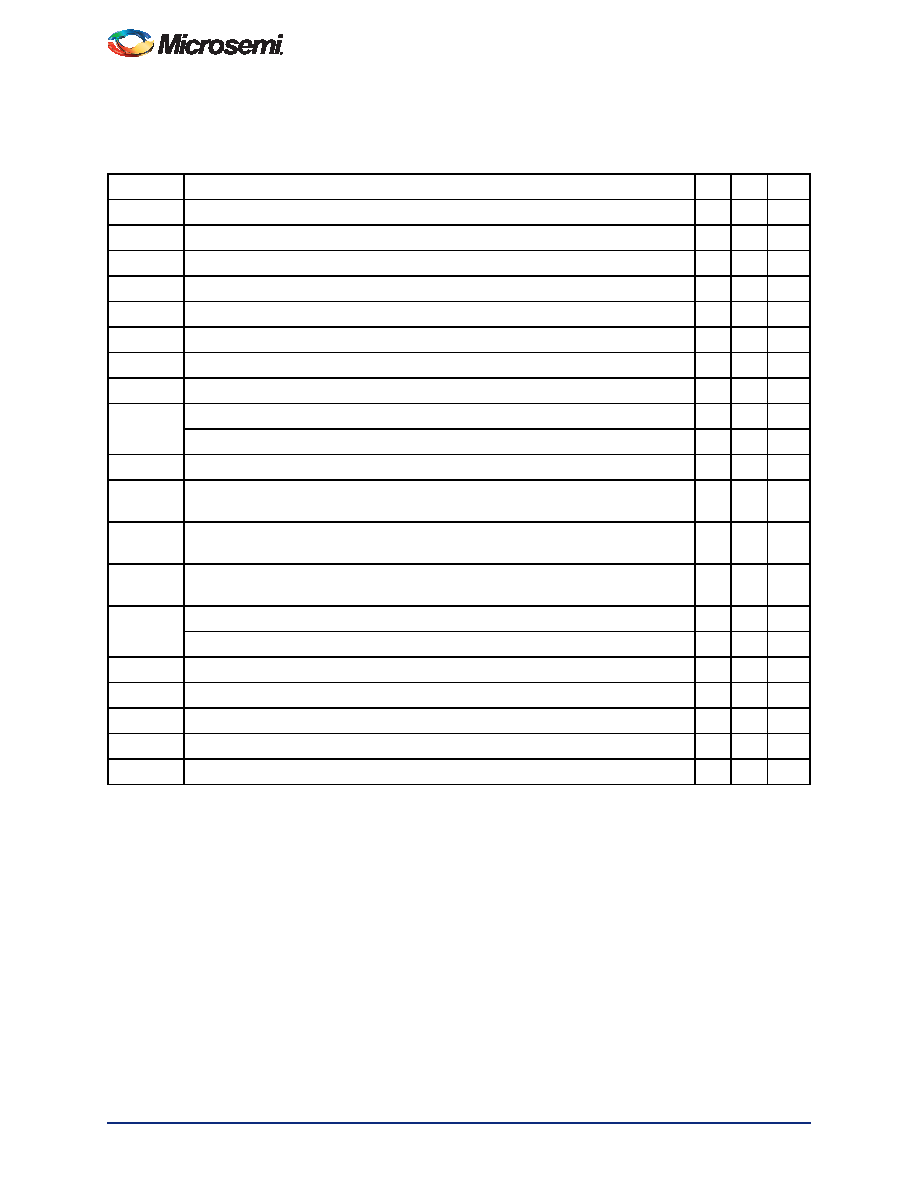

Table 2-214 RAM4K9 鈥� Applies to 1.5 V DC Core Voltage

Commercial-Case Conditions: TJ = 70掳C, Worst-Case VCC = 1.425 V

Parameter

Description

鈥�1

Std. Units

tAS

Address setup time

0.25 0.30

ns

tAH

Address hold time

0.00 0.00

ns

tENS

REN, WEN setup time

0.15 0.17

ns

tENH

REN, WEN hold time

0.10 0.12

ns

tBKS

BLK setup time

0.24 0.28

ns

tBKH

BLK hold time

0.02 0.02

ns

tDS

Input data (DIN) setup time

0.19 0.22

ns

tDH

Input data (DIN) hold time

0.00 0.00

ns

tCKQ1

Clock High to new data valid on DOUT (output retained, WMODE = 0)

1.82 2.14

ns

Clock High to new data valid on DOUT (flow-through, WMODE = 1)

2.40 2.83

ns

tCKQ2

Clock High to new data valid on DOUT (pipelined)

0.91 1.07

ns

tC2CWWL1

Address collision clk-to-clk delay for reliable write after write on same address 鈥�

applicable to closing edge

0.24 0.29

ns

tC2CRWH1

Address collision clk-to-clk delay for reliable read access after write on same

address 鈥� applicable to opening edge

0.20 0.24

ns

tC2CWRH1

Address collision clk-to-clk delay for reliable write access after read on same

address 鈥� applicable to opening edge

0.25 0.30

ns

tRSTBQ

RESET Low to data out Low on DOUT (flow-through)

0.94 1.11

ns

RESET Low to data out Low on DOUT (pipelined)

0.94 1.11

ns

tREMRSTB

RESET removal

0.29 0.34

ns

tRECRSTB

RESET recovery

1.53 1.80

ns

tMPWRSTB RESET minimum pulse width

0.55 0.64

ns

tCYC

Clock cycle time

5.10 5.87

ns

FMAX

Maximum frequency

196 170 MHz

Notes:

1. For more information, refer to the application note Simultaneous Read-Write Operations in Dual-Port SRAM for Flash-

2. For specific junction temperature and voltage supply levels, refer to Table 2-6 on page 2-7 for derating values.

鐩搁棞(gu膩n)PDF璩囨枡 |

PDF鎻忚堪 |

|---|---|

| A3P600L-FG484 | IC FPGA 1KB FLASH 600K 484-FBGA |

| IDT7164S20YG8 | IC SRAM 64KBIT 20NS 28SOJ |

| A40MX02-3PLG68 | IC FPGA MX SGL CHIP 3K 68-PLCC |

| IDT71V124SA10PHG | IC SRAM 1MBIT 10NS 32TSOP |

| A40MX02-3PL68 | IC FPGA MX SGL CHIP 3K 68-PLCC |

鐩搁棞(gu膩n)浠g悊鍟�/鎶€琛�(sh霉)鍙冩暩(sh霉) |

鍙冩暩(sh霉)鎻忚堪 |

|---|---|

| A3P600L-FGG484I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 484-FBGA RoHS:鏄� 椤�(l猫i)鍒�:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸(m茅n)闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€(m茅n)鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤�(l猫i)鍨�:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| A3P600L-PQ208 | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 208-PQFP RoHS:鍚� 椤�(l猫i)鍒�:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸(m茅n)闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€(m茅n)鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤�(l猫i)鍨�:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A3P600L-PQ208I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 208-PQFP RoHS:鍚� 椤�(l猫i)鍒�:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸(m茅n)闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€(m茅n)鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤�(l猫i)鍨�:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

| A3P600L-PQG208 | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 208-PQFP RoHS:鏄� 椤�(l猫i)鍒�:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸(m茅n)闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:90 绯诲垪:ProASIC3 LAB/CLB鏁�(sh霉):- 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):36864 杓稿叆/杓稿嚭鏁�(sh霉):157 闁€(m茅n)鏁�(sh霉):250000 闆绘簮闆诲:1.425 V ~ 1.575 V 瀹夎椤�(l猫i)鍨�:琛ㄩ潰璨艰 宸ヤ綔婧害:-40°C ~ 125°C 灏佽/澶栨:256-LBGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:256-FPBGA锛�17x17锛� |

| A3P600L-PQG208I | 鍔熻兘鎻忚堪:IC FPGA 1KB FLASH 600K 208-PQFP RoHS:鏄� 椤�(l猫i)鍒�:闆嗘垚闆昏矾 (IC) >> 宓屽叆寮� - FPGA锛堢従(xi脿n)鍫�(ch菐ng)鍙法绋嬮杸(m茅n)闄e垪锛� 绯诲垪:ProASIC3L 妯�(bi膩o)婧�(zh菙n)鍖呰:40 绯诲垪:SX-A LAB/CLB鏁�(sh霉):6036 閭忚集鍏冧欢/鍠厓鏁�(sh霉):- RAM 浣嶇附瑷�(j矛):- 杓稿叆/杓稿嚭鏁�(sh霉):360 闁€(m茅n)鏁�(sh霉):108000 闆绘簮闆诲:2.25 V ~ 5.25 V 瀹夎椤�(l猫i)鍨�:琛ㄩ潰璨艰 宸ヤ綔婧害:0°C ~ 70°C 灏佽/澶栨:484-BGA 渚涙噳(y墨ng)鍟嗚ō(sh猫)鍌欏皝瑁�:484-FPBGA锛�27X27锛� |

鐧�(f膩)甯冪穵鎬ラ噰璩�(g貌u)锛�3鍒嗛悩宸﹀彸鎮ㄥ皣寰楀埌鍥炲京(f霉)銆�