參數資料

| 型號: | A1020B-1PLG44C |

| 廠商: | Microsemi SoC |

| 文件頁數: | 33/98頁 |

| 文件大小: | 0K |

| 描述: | IC FPGA 2K GATES 44-PLCC COM |

| 標準包裝: | 27 |

| 系列: | ACT™ 1 |

| LAB/CLB數: | 547 |

| 輸入/輸出數: | 34 |

| 門數: | 2000 |

| 電源電壓: | 4.5 V ~ 5.5 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 70°C |

| 封裝/外殼: | 44-LCC(J 形引線) |

| 供應商設備封裝: | 44-PLCC(16.59x16.59) |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁當前第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁

39

Hi R e l F P GA s

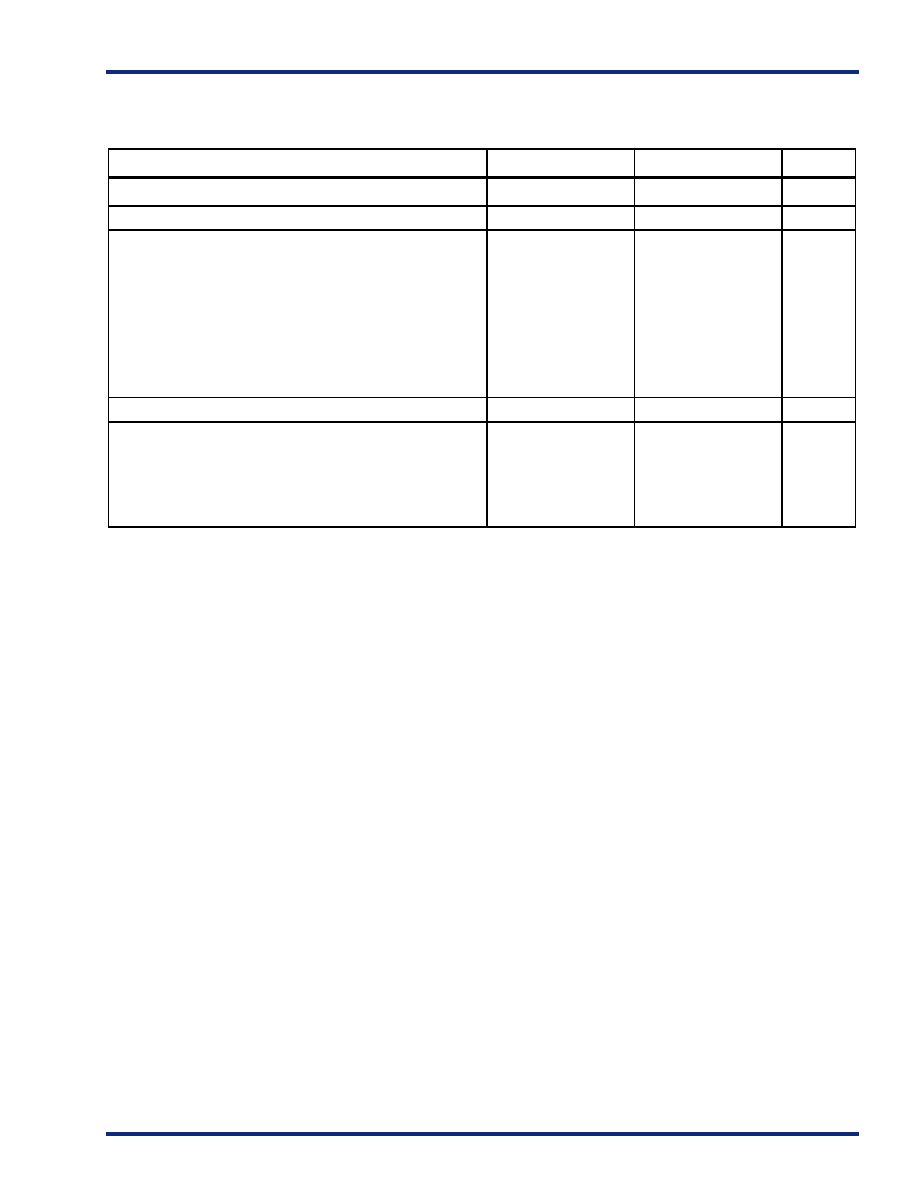

A1 42 5A T i m i n g C har a c t e r i st i c s (continued)

(W or s t - C as e M i l i t a r y Cond i t i o n s , V CC = 4.5 V, TJ = 1 25°C)

‘–1’ Speed

‘Std’ Speed

Parameter

Description

Min.

Max.

Min.

Max.

Units

Routed Array Clock Networks

tRCKH

Input Low to High (FO=64)

5.5

6.4

ns

tRCKL

Input High to Low (FO=64)

6.0

7.0

ns

tRPWH

Min. Pulse Width High (FO=64)

4.9

5.7

ns

tRPWL

Min. Pulse Width Low (FO=64)

4.9

5.7

ns

tRCKSW

Maximum Skew (FO=128)

1.1

1.2

ns

tRP

Minimum Period (FO=64)

10.1

11.6

ns

fRMAX

Maximum Frequency (FO=64)

100

85

MHz

Clock-to-Clock Skews

tIOHCKSW

I/O Clock to H-Clock Skew

0.0

3.0

0.0

3.0

ns

tIORCKSW

I/O Clock to R-Clock Skew

0.0

3.0

0.0

3.0

ns

tHRCKSW

H-Clock to R-Clock Skew

(FO = 64)

(FO = 50% max.)

0.0

1.0

3.0

0.0

1.0

3.0

ns

相關PDF資料 |

PDF描述 |

|---|---|

| A1020B-1PL44C | IC FPGA 2K GATES 44-PLCC COM |

| A54SX16P-TQ144 | IC FPGA SX 24K GATES 144-TQFP |

| A54SX16P-TQG144 | IC FPGA SX 24K GATES 144-TQFP |

| A1010B-1PQG100I | IC FPGA 1200 GATES 100-PQFP IND |

| M7A3P1000-1FG256 | IC FPGA 1KB FLASH 1M 256-FBGA |

相關代理商/技術參數 |

參數描述 |

|---|---|

| A1020B-1PLG44I | 功能描述:IC FPGA 2K GATES 44-PLCC IND RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| A1020B-1PLG68C | 功能描述:IC FPGA 2K GATES 68-PLCC COM RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| A1020B-1PLG68I | 功能描述:IC FPGA 2K GATES 68-PLCC IND RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| A1020B-1PLG84C | 功能描述:IC FPGA 2K GATES 84-PLCC COM RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

| A1020B-1PLG84I | 功能描述:IC FPGA 2K GATES 84-PLCC IND RoHS:是 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:ACT™ 1 標準包裝:40 系列:SX-A LAB/CLB數:6036 邏輯元件/單元數:- RAM 位總計:- 輸入/輸出數:360 門數:108000 電源電壓:2.25 V ~ 5.25 V 安裝類型:表面貼裝 工作溫度:0°C ~ 70°C 封裝/外殼:484-BGA 供應商設備封裝:484-FPBGA(27X27) |

發(fā)布緊急采購,3分鐘左右您將得到回復。