- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄122717 > 9LPRS501SKLF (INTEGRATED DEVICE TECHNOLOGY INC) SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 PDF資料下載

參數(shù)資料

| 型號(hào): | 9LPRS501SKLF |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | SPECIALTY MICROPROCESSOR CIRCUIT, PQCC64 |

| 封裝: | ROHS COMPLIANT, PLASTIC, MLF-64 |

| 文件頁(yè)數(shù): | 14/27頁(yè) |

| 文件大?。?/td> | 228K |

| 代理商: | 9LPRS501SKLF |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)

IDTTM/ICSTM

64-pin CK505 w/Fully Integrated Voltage Regulator + Integrated Series Resistor

1121G—05/19/11

Advance Information

ICS9LPRS501

64-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR + INTEGRATED SERIES RESISTOR

21

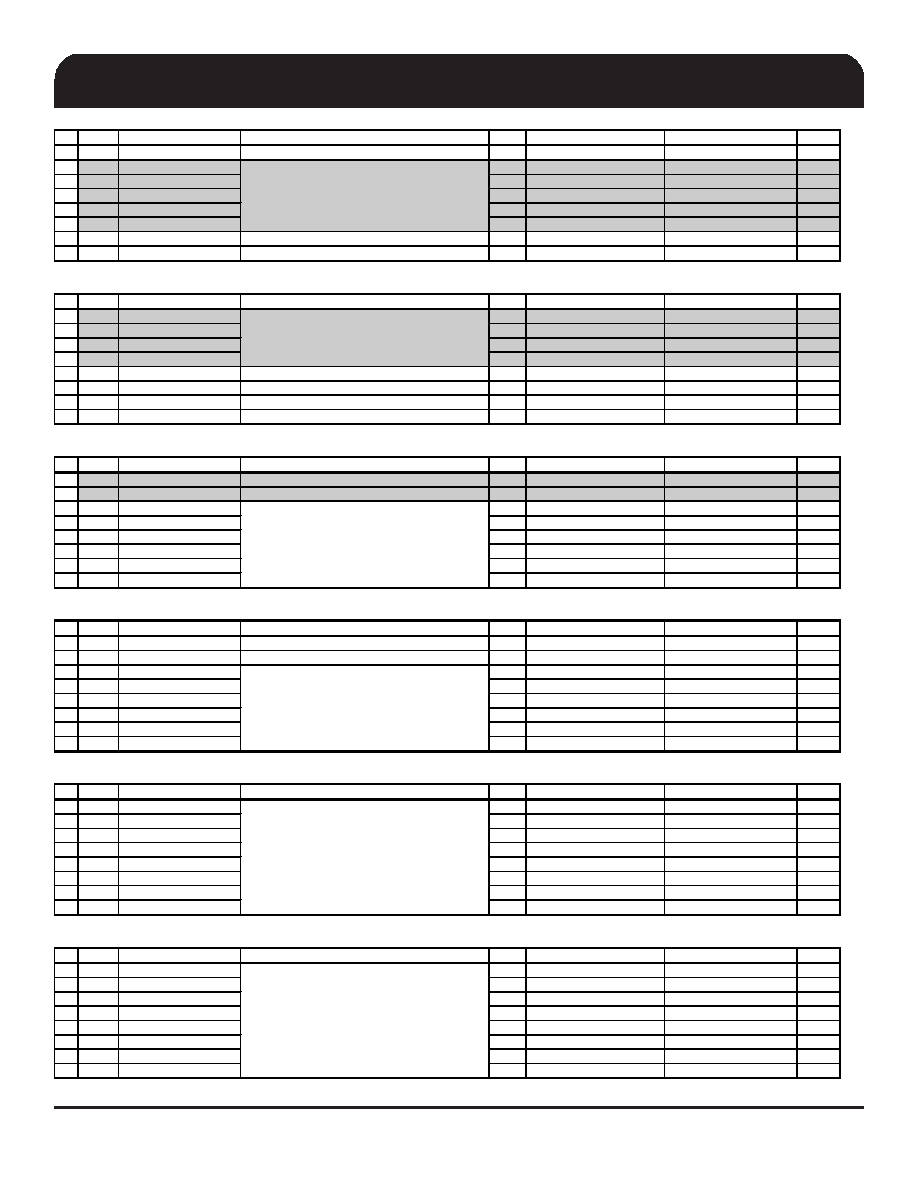

Byte 10 CK505 Rev 0.85 Functions (ICS Rev H Silicon and Higher)

Bit

Pin

Name

Description

Type

0

1

Default

7

SRC5_EN Readback

Readback of SRC5 enable latch

R

CPU/PCI Stop Enabled

SRC5 Enabled

Latch

6

Reserved

RW

TBD

0

5

Reserved

RW

TBD

0

4

Reserved

RW

TBD

0

3

Reserved

RW

TBD

0

2

Reserved

RW

TBD

0

1

CPU 1 Stop Enable

Enables control of CPU1 with CPU_STOP#

RW

Free Running

Stoppable

1

0

CPU 0 Stop Enable

Enables control of CPU 0 with CPU_STOP#

RW

Free Running

Stoppable

1

Byte 11 CK505 Rev 1.0 functions (ICS Rev P silicon and higher)

Bit

Pin

Name

Description

Type

0

1

Default

7

Reserved

RW

TBD

0

6

Reserved

RW

TBD

0

5

Reserved

RW

TBD

0

4

Reserved

RW

TBD

0

3

CPU2_iAMT_EN

Enables CPU2(ITP) output in iAMT state (M1)

RW

Off in iAMT

Free running in iAMT

0

2

CPU1_iAMT_EN

Enables CPU1 output in iAMT state (M1)

RW

Off in iAMT

Free running in iAMT

1

PCIe-Gen2

PCIe-Gen2 status

R

PCIe Gen1 compliant

PCIe Gen2 compliant

0

CPU2 Stop Enable

Enables control of CPU2(ITP) with CPU_STOP#

RW

Free Running

Stoppable

1

Byte 12 Byte Count Register

Bit

Pin

Name

Description

Type

0

1

Default

7

Reserved

RW

0

6

Reserved

RW

0

5

BC5

RW

0

4

BC4

RW

0

3

BC3

RW

1

2

BC2

RW

1

BC1

RW

0

BC0

RW

1

Byte 13 CK505 PLL1 M/N Programming Register

Bit

Pin

Name

Description

Type

0

1

Default

7

N Div8

N Divider 8

RW

-

X

6

N Div9

N Divider 9

RW

-

X

5

M Div5

RW

-

X

4

M Div4

RW

-

X

3

M Div3

RW

-

X

2

M Div2

RW

-

X

1

M Div1

RW

-

X

0

M Div0

RW

-

X

Byte 14 CK505 PLL1 M/N Programming Register

Bit

Pin

Name

Description

Type

0

1

Default

7

N Div7

RW

-

X

6

N Div6

RW

-

X

5

N Div5

RW

-

X

4

N Div4

RW

-

X

3

N Div3

RW

-

X

2

N Div2

RW

-

X

1

N Div1

RW

-

X

0

N Div0

RW

-

X

The decimal representation of M Div (5:0) is equal

to reference divider value. Default at power up =

latch-in or Byte 0 Rom table.

Read Back byte count register

The decimal representation of N Div (9:0) is equal

to VCO divider value. Default at power up = latch-

in or Byte 0 Rom table.

Reserved

Byte 15 CK505 PLL1 Spread Spectrum Control Register

Bit

Pin

Name

Description

Type

0

1

Default

7

SSP7

RW

-

X

6

SSP6

RW

-

X

5

SSP5

RW

-

X

4

SSP4

RW

-

X

3

SSP3

RW

-

X

2

SSP2

RW

-

X

1

SSP1

RW

-

X

0

SSP0

RW

-

X

These Spread Spectrum bits will program the

spread pecentage. Contact ICS for the correct

values.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9LPRS545CFLFT | SPECIALTY MICROPROCESSOR CIRCUIT, PDSO48 |

| 9173B-01CS08LFT | 75 MHz, VIDEO CLOCK GENERATOR, PDSO8 |

| 951601AFLFT | 66.66 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 954201BFLFT | 400 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 935271490512 | 4 CHANNEL(S), 5M bps, SERIAL COMM CONTROLLER, PQCC68 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9LPRS501SKLFT | 功能描述:時(shí)鐘合成器/抖動(dòng)清除器 RoHS:否 制造商:Skyworks Solutions, Inc. 輸出端數(shù)量: 輸出電平: 最大輸出頻率: 輸入電平: 最大輸入頻率:6.1 GHz 電源電壓-最大:3.3 V 電源電壓-最小:2.7 V 封裝 / 箱體:TSSOP-28 封裝:Reel |

| 9LPRS501YGLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:64-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR + INTEGRATED SERIES RESISTOR |

| 9LPRS501YKLFT | 制造商:IDT 制造商全稱:Integrated Device Technology 功能描述:64-PIN CK505 W/FULLY INTEGRATED VOLTAGE REGULATOR + INTEGRATED SERIES RESISTOR |

| 9LPRS502HGLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS502HGLF LOGIC AND TIMING MISC - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS502HGLF Logic and Timing Misc |

| 9LPRS502PGLF | 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS502PGLF PHASED LOCKED LOOP (PLL) - Rail/Tube 制造商:Integrated Device Technology Inc 功能描述:IDT 9LPRS502PGLF Phased Locked Loop (PLL) |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。