- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄164926 > 9763-11 (PEREGRINE SEMICONDUCTOR CORP) 3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications PDF資料下載

參數(shù)資料

| 型號: | 9763-11 |

| 廠商: | PEREGRINE SEMICONDUCTOR CORP |

| 元件分類: | PLL合成/DDS/VCOs |

| 英文描述: | 3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 中文描述: | PLL FREQUENCY SYNTHESIZER, CQCC68 |

| 封裝: | CERAMIC, QFJ-68 |

| 文件頁數(shù): | 4/15頁 |

| 文件大?。?/td> | 351K |

| 代理商: | 9763-11 |

Product Specification

PE9763

2003-2006 Peregrine Semiconductor Corp. All rights reserved.

Document No. 70-0140-02

│ UltraCMOS RFIC Solutions

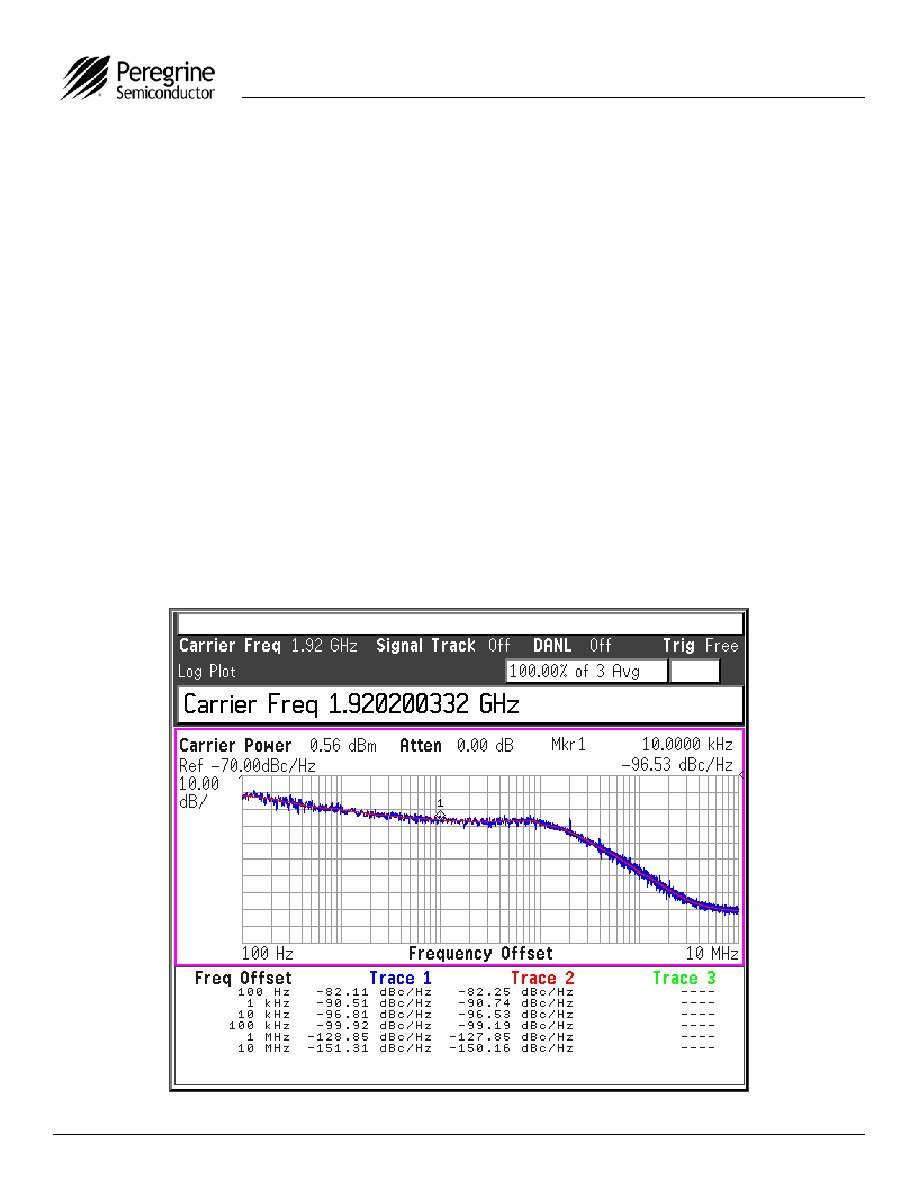

Figure 5. Typical Phase Noise

Phase Detector and Charge Pump

The phase detector is triggered by rising edges

from the main Counter (fp) and the reference

counter (fc). It has two outputs, namely PD_U,

and PD_D. If the divided VCO leads the divided

reference in phase or frequency (fp leads fc),

PD_D pulses “l(fā)ow”. If the divided reference leads

the divided VCO in phase or frequency (fc leads

fp), PD_U pulses “l(fā)ow”. The width of either pulse

is directly proportional to phase offset between the

two input signals, fp and fc.

For the UP and DOWN mode, PD_U and PD_D

drive an active loop filter which controls the VCO

tune voltage. The phase detector gain is equal to

VDD / 2

п.

PD_U pulses cause an increase in VCO fre-

quency and PD_D pulses cause a decrease in

VCO frequency, for a positive Kv VCO.

For the charge pump mode, the phase detector

outputs are used internally to drive a tri-state

charge pump. However, the PD_U, and PD_D out-

put pins will be drive statically to GND. The

charge pump will drive a fixed 2 mA of current.

A lock detect output, LD is also provided, via the

pin Cext. Cext is the logical “NAND” of PD_

U and

PD_

D waveforms, which is driven through a series

2 k

resistor. Connecting Cext to an external

shunt capacitor provides low pass filtering of this

signal. Cext also drives the input of an internal in-

verting comparator with an open drain output.

Thus LD is an “AND” function of PD_

U and PD_D.

A typical phase noise plot is shown below. Phase noise results for “Trace 2” is the average values.

Test Conditions: Fout = 1.9202 GHz, Fcomparison = 20 MHz, MASH 1-1, VDD = 3 V, Temp = 25 C,

Loop bandwidth = 80 KHz.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9765-1523-002 | CABLE TERMINATED, MALE, SSMA CONNECTOR, CRIMP, PLUG |

| 98029-0002 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

| 98029-0003 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

| 98029-0004 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

| 98029-0005 | 6 CONTACT(S), FEMALE, COMBINATION LINE CONNECTOR, SURFACE MOUNT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 97632 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:KUPPLUNG BNC 75 OHM RG59 ROT |

| 97632-00 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 97632-01 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 97632-11 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:3.2 GHz Delta-Sigma modulated Fractional-N Frequency Synthesizer for Low Phase Noise Applications |

| 97633 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:KUPPLUNG BNC 75 OHM RG59 BLAU |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。