- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24864 > 950602CG (INTEGRATED DEVICE TECHNOLOGY INC) 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 PDF資料下載

參數(shù)資料

| 型號: | 950602CG |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時鐘產(chǎn)生/分配 |

| 英文描述: | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 封裝: | 6.10 MM, 0.50 MM PITCH, MO-153, TSSOP-48 |

| 文件頁數(shù): | 1/18頁 |

| 文件大?。?/td> | 233K |

| 代理商: | 950602CG |

Integrated

Circuit

Systems, Inc.

ICS950602

0469B—12/18/02

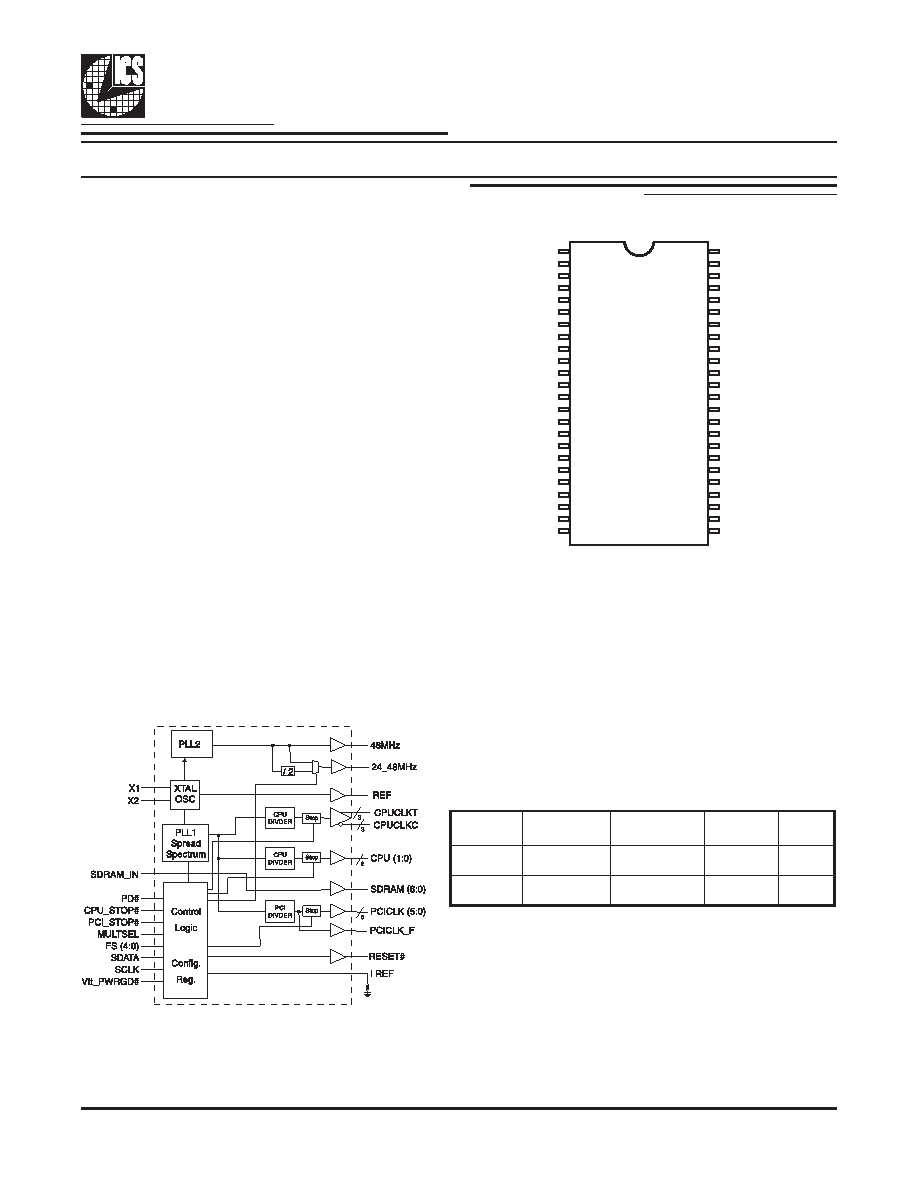

Block Diagram

Pin Configuration

Recommended Application:

VIA Mobile PL133T and PLE133T Chipsets.

Output Features:

2 - CPU clocks @ 2.5V

1 - Pairs of differential CPU clocks @ 3.3V

7 - PCI including 1 free running @ 3.3V

7 - SDRAM @ 3.3V

1 - 48MHz @ 3.3V fixed

1 - 24_48MHz selectable @ 3.3V

2 - REF @ 3.3V, 14.318MHz

Features/Benefits:

Programmable output frequency.

Programmable output divider ratios.

Programmable output rise/fall time.

Programmable output skew.

Programmable spread percentage for EMI control.

Watchdog timer technology to reset system

if system malfunctions.

Programmable watch dog safe frequency.

Support I

2C Index read/write and block read/write

operations.

Uses external 14.318MHz crystal.

Key Specifications:

CPU Output Jitter <200ps

CPU Output Skew <175ps

PCI to PCI Output Skew <500ps

Programmable Timing Control Hub for PII/III

* Internal Pull-up resistor of 120K to VDD

** these inputs have 120K internal pull-down

to GND

48-Pin SSOP & TSSOP

GND

*FS2/REF1

REF0

Vtt_PWRGD#

VDDREF

GND

X1

X2

VDDPCI

*FS4/PCICLK_F

*FS3/PCICLK0

GND

PCICLK1

PCICLK2

PCICLK3

PCICLK4

PCICLK5

SDRAM_IN

*CPU_STOP#

*PCI_STOP#

*PD#

**MULTISEL

GND

SDATA

CPUCLK0

CPUCLK1

VDDCPU_2.5

VDDCPU_3.3

CPUCLKT

CPUCLKC

GND

RESET#

I REF

SDRAM6

GND

SDRAM0

SDRAM1

VDDSDRAM

SDRAM2

SDRAM3

GND

SDRAM4

SDRAM5

VDDSDRAM

AVDD48

48MHz/FS0*

24_48MHz/FS1*

SCLK

ICS950602

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

Host Swing Select Functions

0

L

E

S

I

T

L

U

M

t

e

g

r

a

T

d

r

a

o

B

Z

m

r

e

T

/

e

c

a

r

T

,

R

e

c

n

e

r

e

f

e

R

V

=

f

e

r

I

D

)

r

R

*

3

(

/

t

u

p

t

u

O

t

n

e

r

u

C

Z

@

h

o

V

0s

m

h

o

0

5

,

%

1

2

=

r

R

A

m

0

.

5

=

f

e

r

I

F

E

R

I

*

4

=

h

o

I0

5

@

V

0

.

1

1s

m

h

o

0

5

,

%

1

5

7

4

=

r

R

A

m

2

3

.

2

=

f

e

r

I

F

E

R

I

*

6

=

h

o

I0

5

@

V

7

.

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 950602CF | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 950602CGLFT | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 950602CFLF | 200 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO48 |

| 08056C103JA72A | Circular Connector; MIL SPEC:MIL-C-5015; Body Material:Metal; Series:GT; No. of Contacts:3; Connector Shell Size:22; Connecting Termination:Solder; Circular Shell Style:Box Mount Receptacle; Body Style:Straight |

| 95060 | 1.25 W, SMPS TRANSFORMER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 950602CGLF | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 950602CGLFT | 功能描述:時鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 950609-0004 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 950609-4 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| 95060A360 | 制造商:MISCELLANEOUS 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。