- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄36336 > 935260567118 (NXP SEMICONDUCTORS) COLOR SIGNAL ENCODER, PQFP44 PDF資料下載

參數(shù)資料

| 型號: | 935260567118 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 顏色信號轉(zhuǎn)換 |

| 英文描述: | COLOR SIGNAL ENCODER, PQFP44 |

| 封裝: | PLASTIC, SOT-307, QFP-44 |

| 文件頁數(shù): | 13/59頁 |

| 文件大小: | 232K |

| 代理商: | 935260567118 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁當(dāng)前第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁

2000 Mar 08

20

Philips Semiconductors

Product specication

Digital video encoder

SAA7128H; SAA7129H

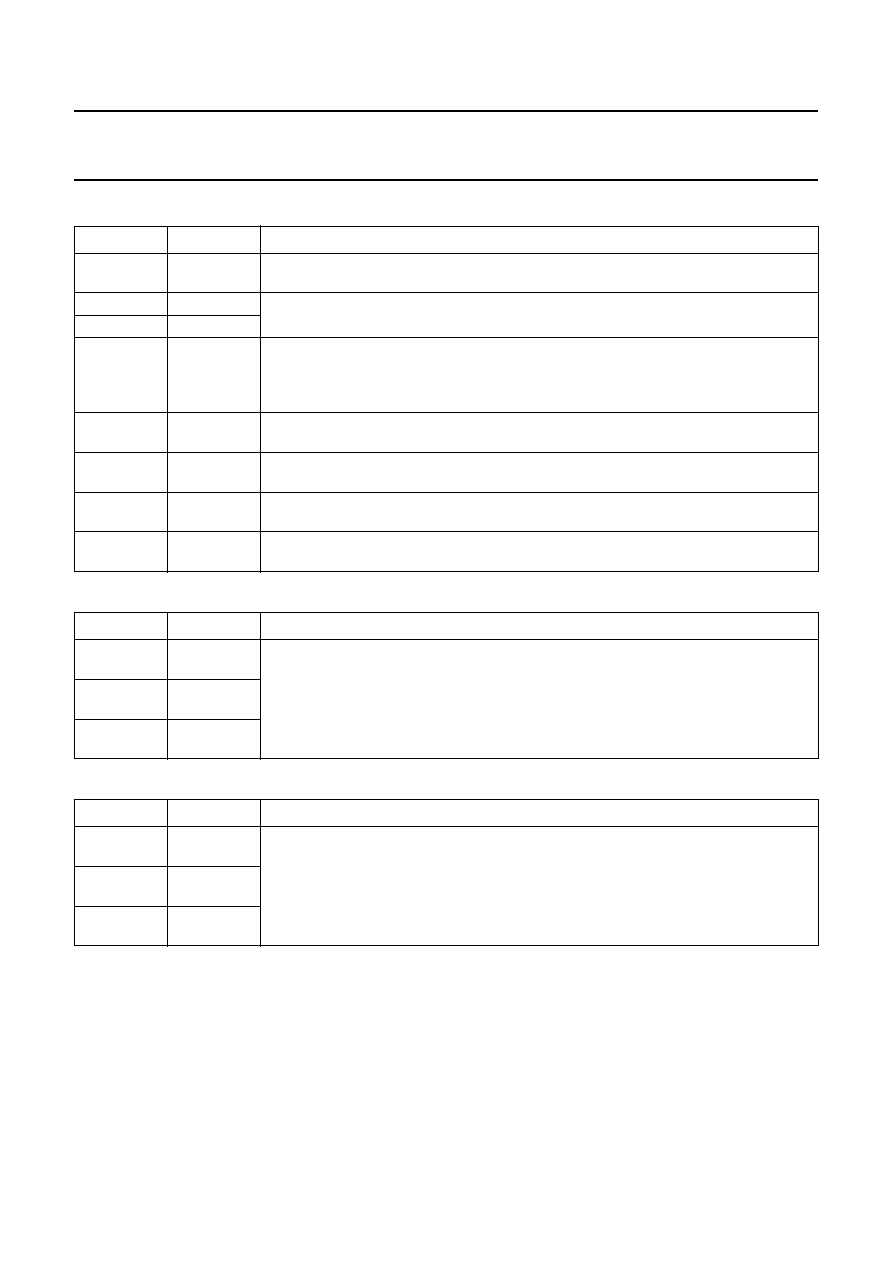

Table 16 Subaddress 3AH

Table 17 Subaddresses 42H to 44H and 48H to 4AH

Table 18 Subaddresses 45H to 47H and 4BH to 4DH

BIT

SYMBOL

DESCRIPTION

7

CBENB

0 = data from input ports is encoded; default state after reset

1 = colour bar with xed colours is encoded

6

These 2 bits are reserved; each must be set to a logic 0.

5

4

SYMP

0 = horizontal and vertical trigger is taken from RCV2 and RCV1 respectively; default

state after reset

1 = horizontal and vertical trigger is decoded out of

“ITU-R BT.656” compatible data at

MPEG port

3

DEMOFF

0 = YCBCR-to-RGB dematrix is active; default state after reset

1=YCBCR-to-RGB dematrix is bypassed

2

CSYNC

0 = CVBS output signal is switched to CVBS DAC; default state after reset

1 = advanced composite sync is switched to CVBS DAC

1

MP2C

0 = input data is 2’s complement from MPEG port fader input

1 = input data is straight binary from MPEG port fader input; default state after reset

0

VP2C

0 = input data is 2’s complement from Video port fader input

1 = input data is straight binary from Video port fader input; default state after reset

ADDRESS

BYTE

DESCRIPTION

42H

48H

KEY1LU

KEY1UU

Key colour 1 lower and upper limits for U, V and Y. If MPEG input signal is within the

limits of key colour 1 the incoming signals at the Video port and MPEG port are added

together according to the equation:

FADE1

× video signal + (1 FADE1) × MPEG signal

Default value of all bytes after reset = 80H.

43H

49H

KEY1LV

KEY1UV

44H

4AH

KEY1LY

KEY1UY

ADDRESS

BYTE

DESCRIPTION

45H

4BH

KEY2LU

KEY2UU

Key colour 2 lower and upper limits for U,V and Y. If MPEG input signal is within the

limits of key colour 2 the incoming signals at the Video port and MPEG port are added

together according to the equation:

FADE2

× video signal + (1 FADE2) × LUT values

Default value of all bytes after reset = 80H.

46H

4CH

KEY2LV

KEY2UV

47H

4DH

KEY2LY

KEY2UY

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935260567151 | COLOR SIGNAL ENCODER, PQFP44 |

| 935260567157 | COLOR SIGNAL ENCODER, PQFP44 |

| 935262600518 | COLOR SIGNAL ENCODER, PQFP44 |

| 935262600557 | COLOR SIGNAL ENCODER, PQFP44 |

| 935262601518 | COLOR SIGNAL ENCODER, PQFP44 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 935261069122 | 制造商:NXP Semiconductors 功能描述:IC SECURITY TRANSPONDER PLLMC |

| 935262025112 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935262217118 | 制造商:NXP Semiconductors 功能描述:Real Time Clock Serial 8-Pin SO T/R |

| 935264217557 | 制造商:NXP Semiconductors 功能描述:SUB ONLY IC |

| 935267356112 | 制造商:NXP Semiconductors 功能描述:IC TEA1507PN |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。