- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24776 > 935165760551 (NXP SEMICONDUCTORS) 8-BIT, 16 MHz, MICROCONTROLLER, PQFP80 PDF資料下載

參數(shù)資料

| 型號: | 935165760551 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 8-BIT, 16 MHz, MICROCONTROLLER, PQFP80 |

| 封裝: | 14 X 20 X 2.70 MM, PLASTIC, QFP-80 |

| 文件頁數(shù): | 48/112頁 |

| 文件大小: | 707K |

| 代理商: | 935165760551 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁當前第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁

1996 Jun 27

40

Philips Semiconductors

Product specication

8-bit microcontroller with on-chip CAN

P8xCE598

13.5.6

INTERRUPT REGISTER (IR)

The Interrupt Register allows the identification of an interrupt source. When one or more bits of this register are set, a

CAN interrupt (SI01) will be indicated to the CPU. All bits are reset by the CAN-controller after this register is read by the

CPU. This register appears to the CPU as a read only memory.

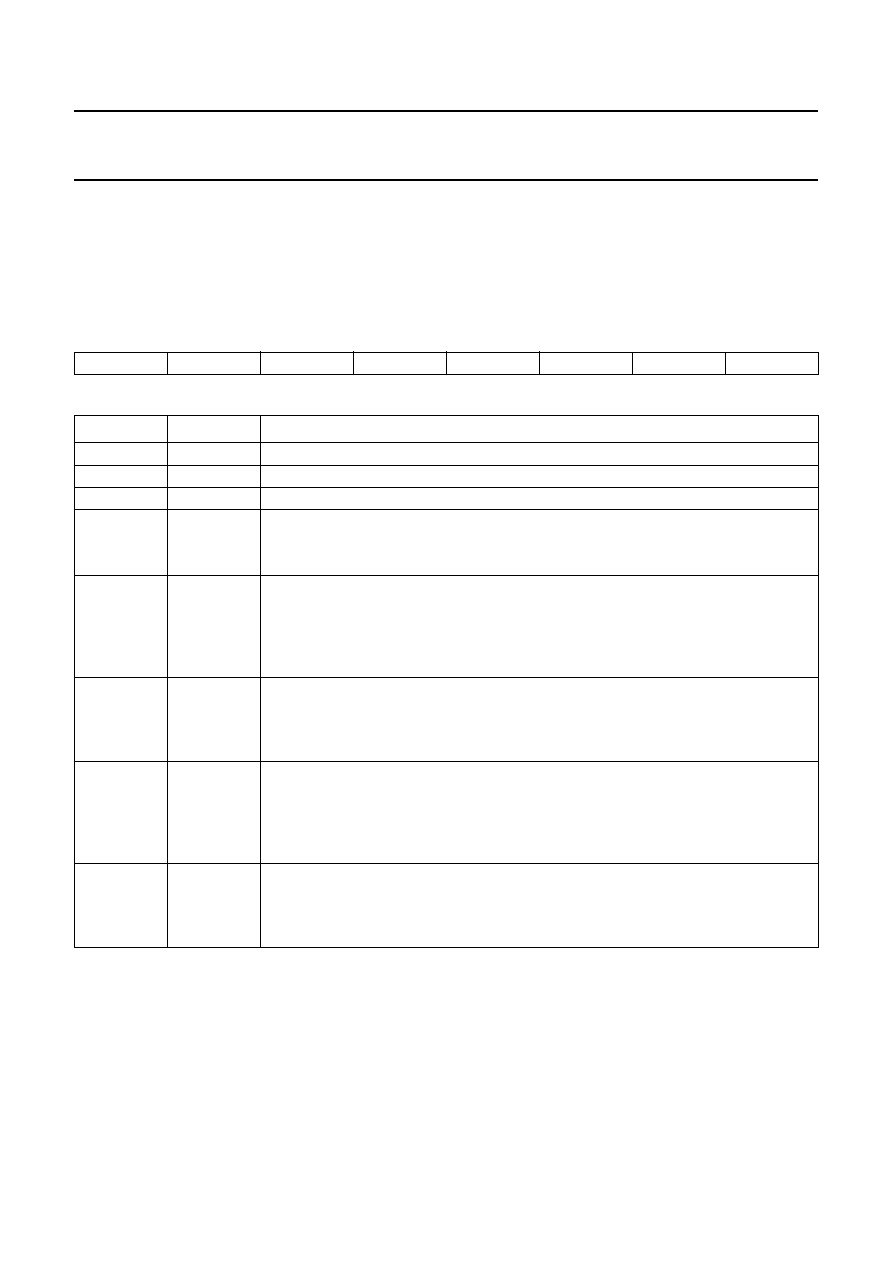

Table 38 Interrupt Register (address 3)

Table 39 Description of the IR bits

Notes

1. Overrun Interrupt bit (if enabled) and Data Overrun bit (see Section 13.5.5) are set at the same time.

2. Receive Interrupt bit (if enabled) and Receive Buffer Status bit (see Section 13.5.5) are set at the same time.

76543210

WUI

OI

EI

TI

RI

BIT

SYMBOL

FUNCTION

7

Reserved.

6

Reserved.

5

Reserved.

4

WUI

Wake-Up Interrupt. The value of WUI is set to:

HIGH (set), when the sleep mode is left. See Section 13.5.4.

LOW (reset), by a read access of the Interrupt Register by the CPU.

3OI

Overrun Interrupt (note 1). The value of OI is set to:

HIGH (set), if both Receive Buffers contain a message and the first byte of another

message should be stored (passed acceptance), and the Overrun Interrupt Enable is

HIGH (enabled).

LOW (reset), by a read access of the Interrupt Register by the CPU.

2EI

Error Interrupt. The value of EI is set to:

HIGH (set), on a change of either the Error Status or Bus Status bits, if the Error

Interrupt Enable is HIGH (enabled). See Section 13.5.5.

LOW (reset), by a read access of the Interrupt Register by the CPU.

1TI

Transmit Interrupt. The value of TI is set to:

HIGH (set), on a change of the Transmit Buffer Access from LOW to HIGH (released)

and

Transmit Interrupt Enable is HIGH (enabled).

LOW (reset), after a read access of the Interrupt Register by the CPU.

0RI

Receive Interrupt (note 2). The value of RBS is set to:

HIGH (set), when a new message is available in the Receive Buffer and the Receive

Interrupt Enable bit is HIGH (enabled).

LOW (reset) automatically by a read access of Interrupt Register by the CPU.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 0673.400 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673.500 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673.600 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673.800 | Axial Lead and Cartridge Fuses - Glass Body |

| 0673001 | Axial Lead and Cartridge Fuses - Glass Body |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 93516-PIX | 制造商:FCI 功能描述: |

| 93517-090001 | 制造商:FCI 功能描述:PCMCIA REV CARD FRAME 9P |

| 93517-150000 | 制造商:FCI 功能描述: |

| 93518097J | 制造商:Fiskars Brands Inc 功能描述:Fiskars 45mm Rotary Blades - Pinking (Fits Models 195800/154570/19680/19583) (Fr |

| 935181002005 | 功能描述:電容套件 HiTmpSilCap Kit 0402 1nF 10nF 33nF BD11V RoHS:否 制造商:Nichicon 電容范圍:10 uF to 680 uF 公差范圍: 電壓范圍:6.3 V to 25 V 產(chǎn)品:Aluminum Organic Polymer Capacitor Kit |

發(fā)布緊急采購,3分鐘左右您將得到回復。