- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24798 > 935051510529 (NXP SEMICONDUCTORS) 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PQCC44 PDF資料下載

參數(shù)資料

| 型號(hào): | 935051510529 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PQCC44 |

| 封裝: | PLASTIC, MO-047AC, SOT-187-2, LCC-44 |

| 文件頁(yè)數(shù): | 14/36頁(yè) |

| 文件大小: | 314K |

| 代理商: | 935051510529 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)當(dāng)前第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)

Philips Semiconductors

Product specification

SC26C92

Dual universal asynchronous receiver/transmitter (DUART)

2000 Jan 31

21

SOPR – Set the Output Port Bits (OPR)

SOPR[7:0] – Ones in the byte written to this register will cause the

corresponding bit positions in the OPR to set to 1. Zeros have no

effect.

ROPR – Reset Output Port Bits (OPR)

ROPR[7:0] – Ones in the byte written to the ROPR will cause the

corresponding bit positions in the OPR to set to 0. Zeros have no effect.

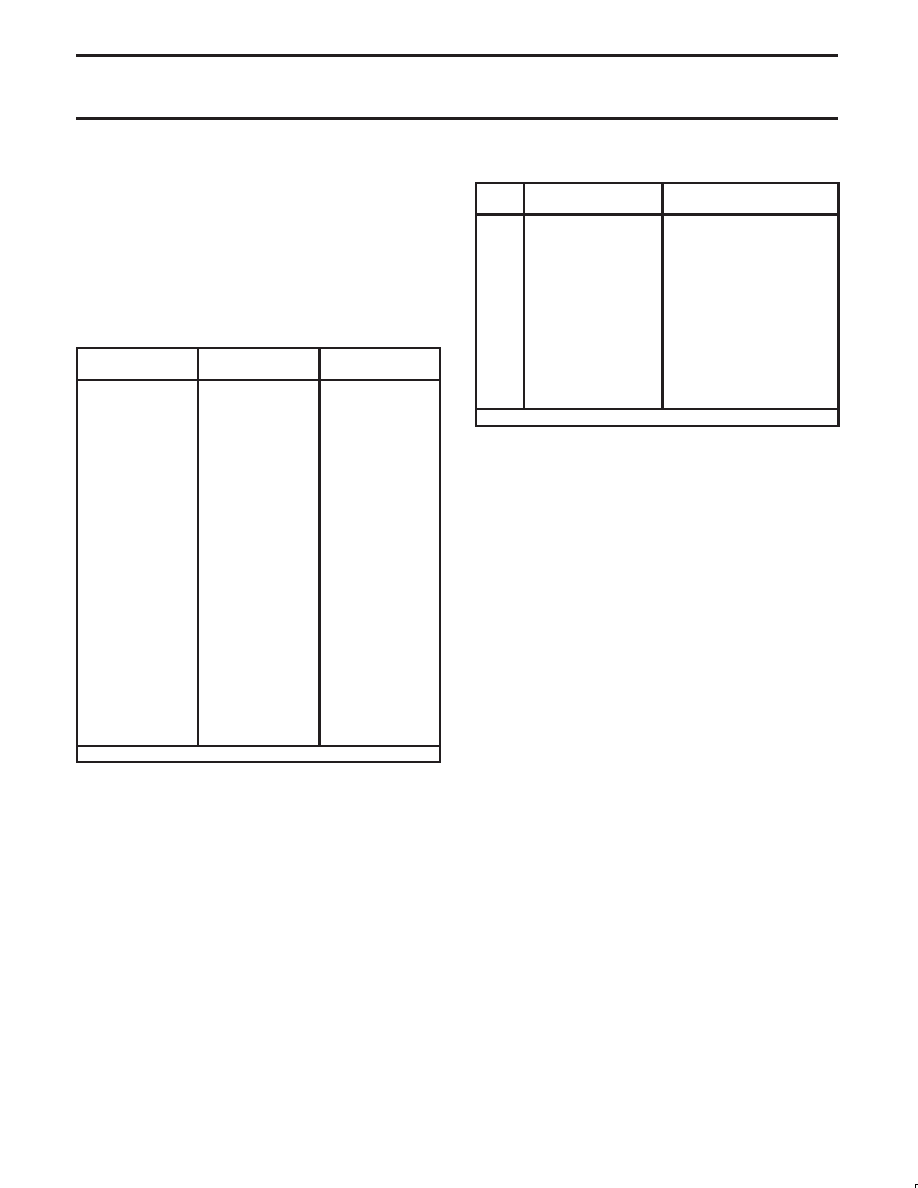

Table 6. Bit Rate Generator Characteristics

Crystal or Clock = 3.6864MHz

NORMAL RATE

(BAUD)

ACTUAL 16X

CLOCK (kHz)

ERROR (%)

50

0.8

0

75

1.2

0

110

1.759

-0.069

134.5

2.153

0.059

150

2.4

0

200

3.2

0

300

4.8

0

600

9.6

0

1050

16.756

-0.260

1200

19.2

0

1800

28.8

0

2000

32.056

0.175

2400

38.4

0

4800

76.8

0

7200

115.2

0

9600

153.6

0

14.4K

230.4

0

19.2K

307.2

0

28.8K

460.8

0

38.4K

614.4

0

57.6K

921.6

0

115.2K

1843.2K

0

230.4K

3686.4K

0

NOTE: Duty cycle of 16X clock is 50%

± 1%.

Asynchronous UART communications can tolerate frequency error

of 4.1% to 6.7% in a “clean” communications channel. The percent

of error changes as the character length changes. The above

percentages range from 5 bits not parity to 8 bits with parity and one

stop bit. The error with 8 bits no parity and one stop bit is 4.6%. If a

stop bit length of 9/16 is used, the error tolerance will approach 0

due to a variable error of up to 1/16 bit time in receiver clock phase

alignment to the start bit.

ACR – Auxiliary Control Register

ACR[7] – Baud Rate Generator Set Select

This bit selects one of two sets of baud rates to be generated by the

BRG (see Table 5).

The selected set of rates is available for use by the Channel A and

B receivers and transmitters as described in CSRA and CSRB.

Baud rate generator characteristics are given in Table 6.

Table 7. ACR 6:4 Field Definition

ACR

6:4

MODE

CLOCK SOURCE

000

Counter

External (IP2)

001

Counter

TxCA – 1X clock of Channel A

transmitter

010

Counter

TxCB – 1X clock of Channel B

transmitter

011

Counter

Crystal or external clock

(X1/CLK) divided by 16

100

Timer (square wave)

External (IP2)

101

Timer (square wave)

External (IP2) divided by 16

110

Timer (square wave)

Crystal or external clock

(X1/CLK)

111

Timer (square wave)

Crystal or external clock

(X1/CLK) divided by 16

NOTE: The timer mode generates a squarewave.

ACR[6:4] – Counter/Timer Mode And Clock Source Select

This field selects the operating mode of the counter/timer and its

clock source as shown in Table 7.

ACR[3:0] – IP3, IP2, IP1, IP0 Change-of-State Interrupt Enable

This field selects which bits of the input port change register (IPCR)

cause the input change bit in the interrupt status register (ISR[7]) to

be set. If a bit is in the ‘on’ state the setting of the corresponding bit

in the IPCR will also result in the setting of ISR[7], which results in

the generation of an interrupt output if IMR[7] = 1. If a bit is in the

‘off’ state, the setting of that bit in the IPCR has no effect on ISR[7].

IPCR – Input Port Change Register

IPCR[7:4] – IP3, IP2, IP1, IP0 Change-of-State

These bits are set when a change-of-state, as defined in the input

port section of this data sheet, occurs at the respective input pins.

They are cleared when the IPCR is read by the CPU. A read of the

IPCR also clears ISR[7], the input change bit in the interrupt status

register. The setting of these bits can be programmed to generate

an interrupt to the CPU.

IPCR[3:0] – IP3, IP2, IP1, IP0 Change-of-State

These bits provide the current state of the respective inputs. The

information is unlatched and reflects the state of the input pins at the

time the IPCR is read.

ISR – Interrupt Status Register

This register provides the status of all potential interrupt sources.

The contents of this register are masked by the Interrupt Mask

Register (IMR). If a bit in the ISR is a ‘1’ and the corresponding bit

in the IMR is also a ‘1’, the INTRN output will be asserted (Low). If

the corresponding bit in the IMR is a zero, the state of the bit in the

ISR has no effect on the INTRN output. Note that the IMR does not

mask the reading of the ISR – the true status will be provided

regardless of the contents of the IMR. The contents of this register

are initialized to H‘00’ when the DUART is reset.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 935263028528 | 2 CHANNEL(S), 1M bps, SERIAL COMM CONTROLLER, PQFP44 |

| 07-MX-24 | LEITERPLATTENRELAIS STANDARD 24VDC |

| 935249960112 | LVC/LCX/Z SERIES, QUAD 2-INPUT NAND GATE, PDSO14 |

| 07-MX-5 | LEITERPLATTENRELAIS STANDARD 5VDC |

| 07-MX-04S | LEITERPLATTENRELAIS STANDARD FASSUNG |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9350524523211N | 制造商:ESSEX 功能描述:ESSEX 32V/DC |

| 9350569 | 制造商:WIKA INSTRUMENTS 功能描述:1/8,1/4 GAUGE |

| 93505A180 | 制造商:MISC. SPCR/STNDF/HND 功能描述: |

| 93505A43 | 制造商:FLORIDA MISC. 功能描述: 制造商:Florida Misc. 功能描述: |

| 93505A435 | 制造商:FLORIDA MISC. 功能描述: 制造商:Florida Misc. 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。