- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24768 > 933861310623 (NXP SEMICONDUCTORS) F/FAST SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 PDF資料下載

參數(shù)資料

| 型號: | 933861310623 |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 鎖存器 |

| 英文描述: | F/FAST SERIES, DUAL NEGATIVE EDGE TRIGGERED J-K FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 封裝: | 3.90 MM, PLASTIC, MS-012AB, SOT-108-1, SO-14 |

| 文件頁數(shù): | 5/10頁 |

| 文件大?。?/td> | 91K |

| 代理商: | 933861310623 |

Philips Semiconductors

Product specification

74F113

Dual J-K negative edge-triggered flip-flops

without reset

1996 Mar 14

4

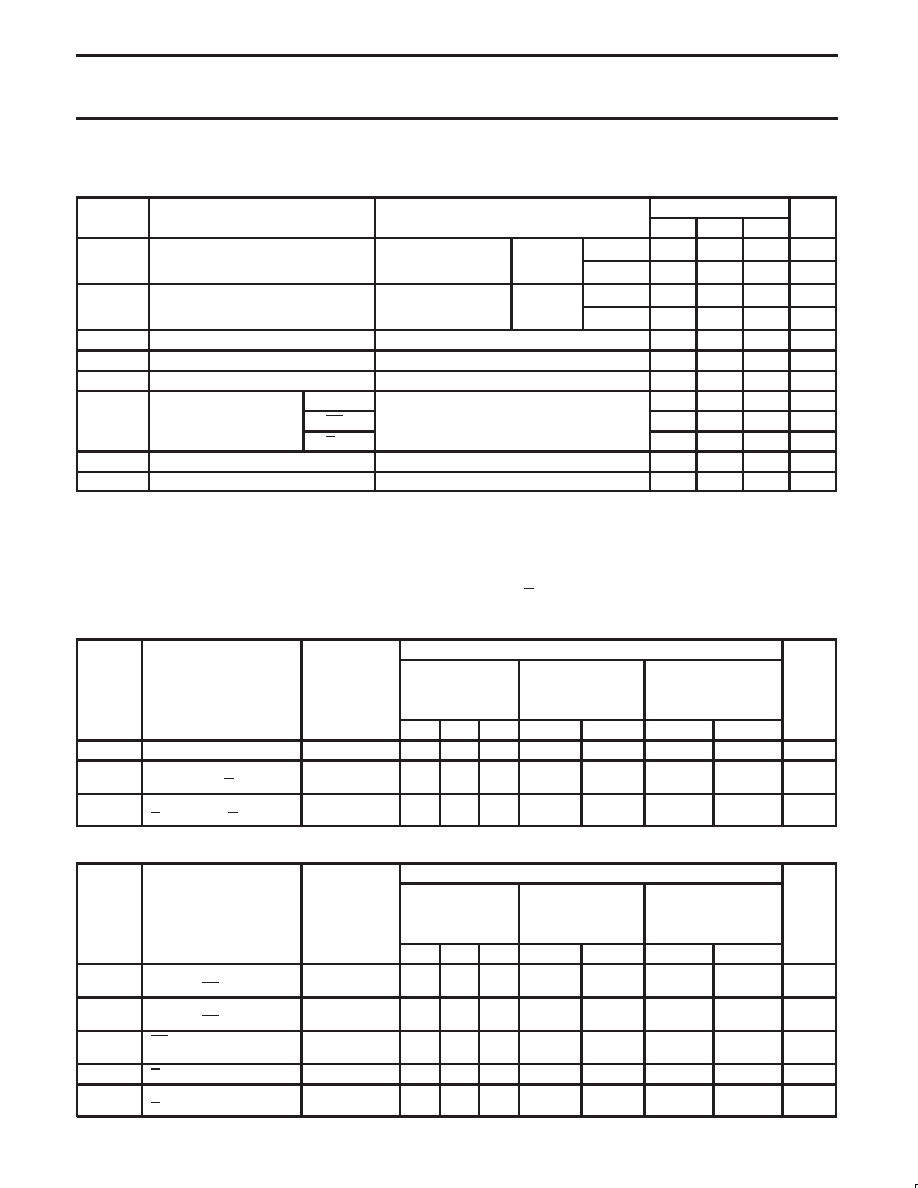

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

PARAMETER

TEST CONDITIONS1

LIMITS

UNIT

SYMBOL

PARAMETER

TEST CONDITIONS1

MIN

TYP2

MAX

UNIT

VO

High level output voltage

VCC = MIN, VIL = MAX,

IO = MAX

±10%V

CC

2.5

V

VOH

High-level output voltage

VCC

MIN, VIL

MAX,

VIH = MIN

IOH = MAX

±5%V

CC

2.7

3.4

V

VO

Low level output voltage

VCC = MIN, VIL = MAX,

IO = MAX

±10%V

CC

0.30

0.50

V

VOL

Low-level output voltage

VCC

MIN, VIL

MAX,

VIH = MIN

IOL = MAX

±5%V

CC

0.30

0.50

V

VIK

Input clamp voltage

VCC = MIN, II = IIK

–0.73

–1.2

V

II

Input current at maximum input voltage

VCC = MAX, VI = 7.0V

100

A

IIH

High-level input current

VCC = MAX, VI = 2.7V

20

A

Jn, Kn

–0.6

mA

IIL

Low-level input current

CPn

VCC = MAX, VI = 0.5V

–2.4

mA

SDn

–3.0

mA

IOS

Short-circuit output current3

VCC = MAX

-60

–150

mA

ICC

Supply current4 (total)

VCC = MAX

15

21

mA

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at VCC = 5V, Tamb = 25°C.

3. Not more than one output should be shorted at a time. For testing IOS, the use of high-speed test apparatus and/or sample-and-hold

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a high output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, IOS tests should be performed last.

4. Measure ICC with the clock input grounded and all outputs open, then with Q and Q outputs high in turn.

AC ELECTRICAL CHARACTERISTICS

LIMITS

SYMBOL

PARAMETER

TEST

CONDITION

VCC = +5.0V

Tamb = +25°C

CL = 50pF

RL = 500

VCC = +5.0V ± 10%

Tamb = 0°C to +70°C

CL = 50pF

RL = 500

VCC = +5.0V ± 10%

Tamb = –40°C to +85°C

CL = 50pF

RL = 500

UNIT

MIN

TYP

MAX

MIN

MAX

MIN

MAX

fmax

Maximum clock frequency

Waveform 1

85

100

80

ns

tPLH

tPHL

Propagation delay

CPn to Qn or Qn

Waveform 1

2.0

4.0

6.0

2.0

7.0

2.0

7.5

7.0

ns

tPLH

tPHL

Propagation delay

SDn, to Qn or Qn

Waveform 2

2.0

4.5

6.5

2.0

7.5

2.0

8.0

7.5

ns

AC SETUP REQUIREMENTS

LIMITS

SYMBOL

PARAMETER

TEST

CONDITION

VCC = +5.0V

Tamb = +25°C

CL = 50pF

RL = 500

VCC = +5.0V ± 10%

Tamb = 0°C to +70°C

CL = 50pF

RL = 500

VCC = +5.0V ± 10%

Tamb = –40°C to +85°C

CL = 50pF

RL = 500

UNIT

MIN

TYP

MAX

MIN

MAX

MIN

MAX

tsu (H)

tsu(L)

Setup time, high or low

Jn, Kn to CPn

Waveform 1

4.0

3.5

5.0

4.0

5.0

4.5

ns

th (H)

th (L)

Hold time, high or low

Jn, Kn to CPn

Waveform 1

0.0

ns

tw (H)

tw (L)

CP pulse width,

high or low

Waveform 1

4.5

5.0

ns

tw (L)

SDn pulse width, low

Waveform 2

4.5

5.0

ns

trec

Recovery time

SDn to CPn

Waveform 2

4.5

5.0

ns

相關PDF資料 |

PDF描述 |

|---|---|

| 935037700602 | F/FAST SERIES, HEX 2-INPUT AND GATE, PDSO20 |

| 935037600623 | F/FAST SERIES, HEX 2-INPUT AND GATE, PDSO20 |

| 935037600602 | F/FAST SERIES, HEX 2-INPUT AND GATE, PDSO20 |

| 935037700623 | F/FAST SERIES, HEX 2-INPUT AND GATE, PDSO20 |

| 935037710623 | F/FAST SERIES, HEX 2-INPUT OR GATE, PDSO20 |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 933871-1 | 制造商:TE Connectivity 功能描述:GUIDE, MODIFIED - Bulk |

| 9-338728-0 | 功能描述:集管和線殼 MICROM. MOB SMD CON RoHS:否 產(chǎn)品種類:1.0MM Rectangular Connectors 產(chǎn)品類型:Headers - Pin Strip 系列:DF50 觸點類型:Pin (Male) 節(jié)距:1 mm 位置/觸點數(shù)量:16 排數(shù):1 安裝風格:SMD/SMT 安裝角:Right 端接類型:Solder 外殼材料:Liquid Crystal Polymer (LCP) 觸點材料:Brass 觸點電鍍:Gold 制造商:Hirose Connector |

| 933873-1 | 制造商:TE Connectivity 功能描述:PLATE, CYL MTG. - Bulk |

| 933879-8 | 制造商:TE Connectivity 功能描述:WHEEL, WIRE SELECTOR - Bulk |

| 933879-9 | 制造商:TE Connectivity 功能描述:WHEEL, WIRE SELECTOR - Bulk |

發(fā)布緊急采購,3分鐘左右您將得到回復。