- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄24624 > 9250BF-27 (INTEGRATED DEVICE TECHNOLOGY INC) 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 PDF資料下載

參數(shù)資料

| 型號(hào): | 9250BF-27 |

| 廠商: | INTEGRATED DEVICE TECHNOLOGY INC |

| 元件分類: | 時(shí)鐘產(chǎn)生/分配 |

| 英文描述: | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 封裝: | 0.300 INCH, 0.025 INCH PITCH, MO-118, SSOP-56 |

| 文件頁數(shù): | 13/17頁 |

| 文件大小: | 221K |

| 代理商: | 9250BF-27 |

5

ICS9250-27

0395D—10/25/05

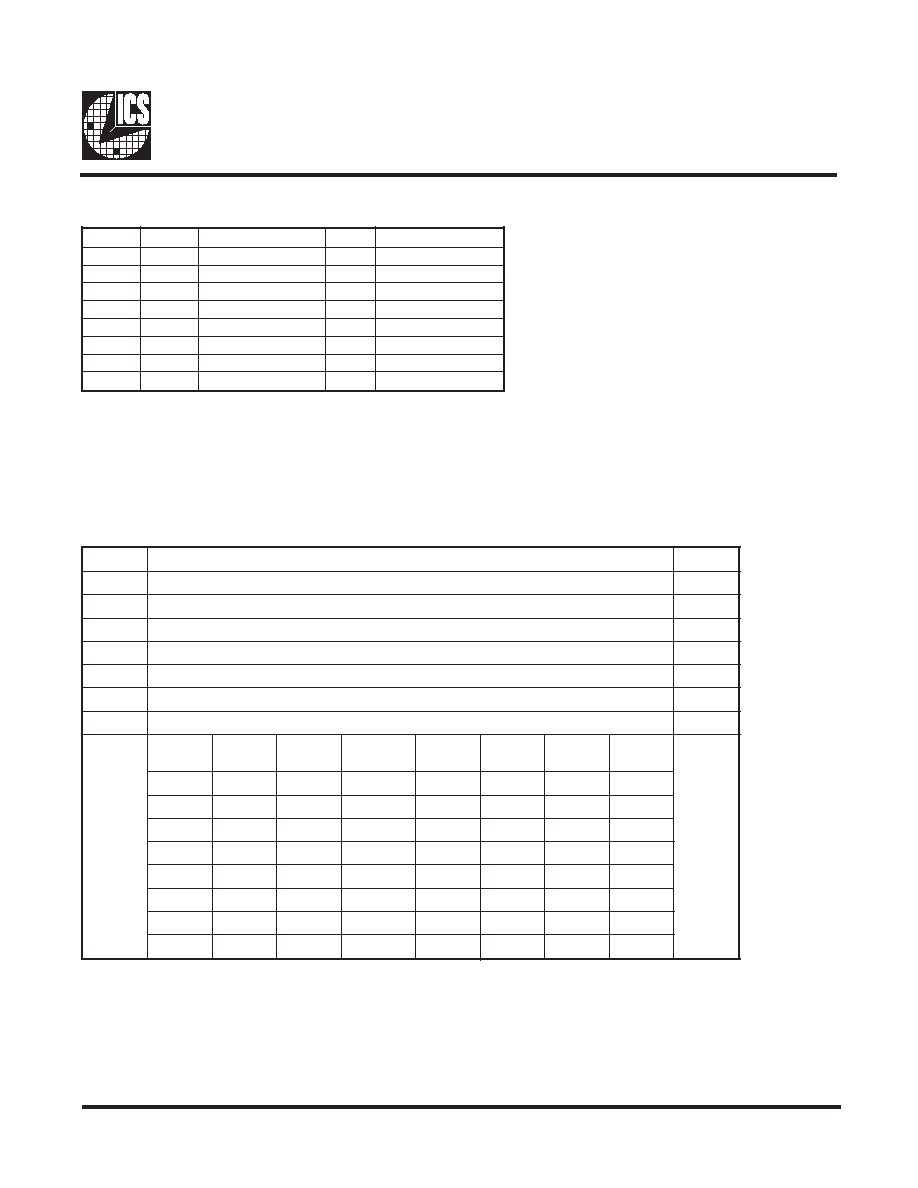

Byte 3: ICS Reserved Functionality and frequency select register (Default as noted in PWD)

Note 1: For system operation, the BSEL lines of the CPU will program FS0, FS2 for the appropriate CPU speed, always with

SDRAM = 100MHz. After BIOS verifies the SDRAM is PC133 speed, then bit 0 can be written from the default 0 to

1 to change the SDRAM output frequency from 100MHz to 133MHz. This will only change if the CPU is at the

133MHz FSB speed as shown in this table. The CPU, 3v66, PCI, and IOAPIC clocks will be glitch free during this

transition, and only SDRAM will change.

Note 2: "ICS RESERVED BITS" must be writtern as "O".

Note3: Undefined bits can be written either as "1 or 0"

t

i

Bn

o

i

t

p

i

t

c

s

e

DD

W

P

7

t

i

B)

2

e

t

o

N

(

t

i

b

d

e

v

r

e

s

e

R

S

C

I

0

6

t

i

B)

2

e

t

o

N

(

t

i

b

d

e

v

r

e

s

e

R

S

C

I

0

5

t

i

B)

2

e

t

o

N

(

t

i

b

d

e

v

r

e

s

e

R

S

C

I

0

4

t

i

B)

2

e

t

o

N

(

t

i

b

d

e

v

r

e

s

e

R

S

C

I

0

3

t

i

B)

2

e

t

o

N

(

t

i

b

d

e

v

r

e

s

e

R

S

C

I

0

2

t

i

B)

3

e

t

o

N

(

t

i

b

d

e

n

i

f

e

d

n

U

X

1

t

i

B)

3

e

t

o

N

(

t

i

b

d

e

n

i

f

e

d

n

U

X

0

t

i

B

0

t

i

B0

S

F1

S

F

K

L

C

U

P

C

z

H

M

A

R

D

S

z

H

M

6

V

3

z

H

M

K

L

C

I

C

P

z

H

M

C

I

P

A

O

I

z

H

M

0

1

e

t

o

N

000

6

.

6

60

.

0

16

6

.

6

63

3

.

3

33

3

.

3

01

0

.

0

10

.

0

16

6

.

6

63

3

.

3

33

3

.

3

00

1

2

3

.

3

12

3

.

3

16

6

.

6

63

3

.

3

33

3

.

3

01

1

2

3

.

3

10

.

0

16

6

.

6

63

3

.

3

33

3

.

3

10

0

6

.

6

60

.

0

16

6

.

6

63

3

.

3

33

3

.

3

11

0

.

0

10

.

0

16

6

.

6

63

3

.

3

33

3

.

3

10

1

2

3

.

3

12

3

.

3

16

6

.

6

63

3

.

3

33

3

.

3

111

2

3

.

3

12

3

.

3

16

6

.

6

63

3

.

3

33

3

.

3

Byte 2: Control Register

(1 = enable, 0 = disable)

Notes:

1. Inactive means outputs are held LOW and are disabled from switching. These outputs are designed to be

configured at power-on and are not expected to be configured during the normal modes of operation.

2. PWD = Power on Default

3. Undefined bit can be wirtten with either a "1" or "0".

t

i

B#

n

i

Pe

m

a

ND

W

Pn

o

i

t

p

i

r

c

s

e

D

7

t

i

B9

)

P

G

A

(

2

-

6

V

31

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

6

t

i

B0

25

K

L

C

I

C

P1

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

5

t

i

B9

14

K

L

C

I

C

P1

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

4

t

i

B8

13

K

L

C

I

C

P1

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

3

t

i

B6

12

K

L

C

I

C

P1

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

2

t

i

B5

11

K

L

C

I

C

P1

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

1

t

i

B3

10

K

L

C

I

C

P1

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

0

t

i

B-

t

i

b

d

e

n

i

f

e

d

n

UX

)

e

v

i

t

c

a

n

I

/

e

v

i

t

c

A

(

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 9250BF-27LFT | 133 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 051-928-9029 | RF Coaxial Connectors |

| 9250BF-28-T | 133.32 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250CF-10 | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

| 9250CF-10LF | 100 MHz, PROC SPECIFIC CLOCK GENERATOR, PDSO56 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 9250BF27LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Dual 56-Pin SSOP Tube |

| 9250BF-27LF | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9250BF-27LFT | 功能描述:時(shí)鐘發(fā)生器及支持產(chǎn)品 RoHS:否 制造商:Silicon Labs 類型:Clock Generators 最大輸入頻率:14.318 MHz 最大輸出頻率:166 MHz 輸出端數(shù)量:16 占空比 - 最大:55 % 工作電源電壓:3.3 V 工作電源電流:1 mA 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:QFN-56 |

| 9250BF-28LF | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP Tube |

| 9250BF-28LFT | 制造商:Integrated Device Technology Inc 功能描述:PLL Frequency Generator Single 56-Pin SSOP T/R |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。