- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375089 > 74VHC161 (Fairchild Semiconductor Corporation) Quadruple 2-Input Positive-NAND Gates 14-TSSOP -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | 74VHC161 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | Quadruple 2-Input Positive-NAND Gates 14-TSSOP -40 to 85 |

| 中文描述: | 4位二進制計數(shù)器的異步清除 |

| 文件頁數(shù): | 2/10頁 |

| 文件大?。?/td> | 123K |

| 代理商: | 74VHC161 |

www.fairchildsemi.com

2

7

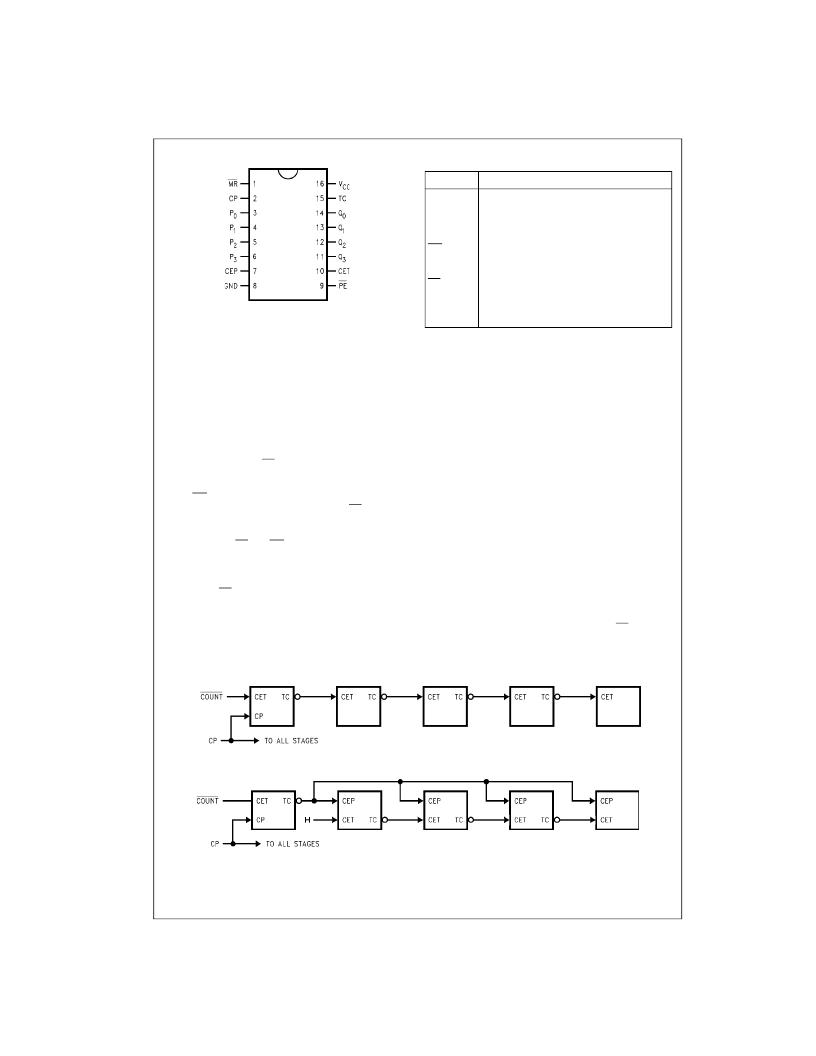

Connection Diagram

Pin Descriptions

Functional Description

The VHC161 counts in modulo-16 binary sequence. From

state 15 (HHHH) it increments to state 0 (LLLL). The clock

inputs of all flip-flops are driven in parallel through a clock

buffer. Thus all changes of the Q outputs (except due to

Master Reset of the VHC161) occur as a result of, and syn-

chronous with, the LOW-to-HIGH transition of the CP input

signal. The circuits have four fundamental modes of opera-

tion, in order of precedence: asynchronous reset, parallel

load, count-up and hold. Five control inputs

—

Master

Reset, Parallel Enable (PE), Count Enable Parallel (CEP)

and Count Enable Trickle (CET)

—

determine the mode of

operation, as shown in the Mode Select Table. A LOW sig-

nal on MR overrides all other inputs and asynchronously

forces all outputs LOW. A LOW signal on PE overrides

counting and allows information on the Parallel Data (P

n

)

inputs to be loaded into the flip-flops on the next rising

edge of CP. With PE and MR HIGH, CEP and CET permit

counting when both are HIGH. Conversely, a LOW signal

on either CEP or CET inhibits counting.

The VHC161 uses D-type edge-triggered flip-flops and

changing the PE, CEP and CET inputs when the CP is in

either state does not cause errors, provided that the recom-

mended setup and hold times, with respect to the rising

edge of CP, are observed.

The Terminal Count (TC) output is HIGH when CET is

HIGH and counter is in state 15. To implement synchro-

nous multistage counters, the TC outputs can be used with

the CEP and CET inputs in two different ways.

Figure 1

shows the connections for simple ripple carry, in

which the clock period must be longer than the CP to TC

delay of the first stage, plus the cumulative CET to TC

delays of the intermediate stages, plus the CET to CP

setup time of the last stage. This total delay plus setup time

sets the upper limit on clock frequency. For faster clock

rates, the carry lookahead connections shown in

Figure 2

are recommended. In this scheme the ripple delay through

the intermediate stages commences with the same clock

that causes the first stage to tick over from max to min to

start its final cycle. Since this final cycle requires 16 clocks

to complete, there is plenty of time for the ripple to progress

through the intermediate stages. The critical timing that lim-

its the clock period is the CP to TC delay of the first stage

plus the CEP to CP setup time of the last stage. The TC

output is subject to decoding spikes due to internal race

conditions and is therefore not recommended for use as a

clock or asynchronous reset for flip-flops, registers or

counters.

Logic Equations: Count Enable

=

CEP

CET

PE

TC

=

Q

0

Q

1

Q

2

Q

3

CET

FIGURE 1. Multistage Counter with Ripple Carry

FIGURE 2. Multistage Counter with Lookahead Carry

Pin Names

Description

CEP

Count Enable Parallel Input

CET

Count Enable Trickle Input

CP

Clock Pulse Input

MR

Asynchronous Master Reset Input

P

0

–

P

3

PE

Parallel Data Inputs

Parallel Enable Inputs

Q

0

–

Q

3

TC

Flip-Flop Outputs

Terminal Count Output

相關PDF資料 |

PDF描述 |

|---|---|

| 74VHC161M | 4-Bit Binary Counter with Asynchronous Clear |

| 74VHC161MTC | Quadruple 2-Input Positive-NOR Gates 14-SOIC -40 to 85 |

| 74VHC161N | Quadruple 2-Input Positive-NOR Gates 14-SOIC -40 to 85 |

| 74VHC161SJ | 4-Bit Binary Counter with Asynchronous Clear |

| 74VHC161MTCX | COUNTER|UP|4-BIT BINARY|HC-CMOS|TSSOP|16PIN|PLASTIC |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 74VHC161284 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:IEEE 1284 Transceiver |

| 74VHC161284MEA | 功能描述:總線收發(fā)器 IEEE 16284 Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74VHC161284MEA.DEL | 制造商:Fairchild Semiconductor Corporation 功能描述:IEEE 1284 Transceiver 13TX 12RX 48-Pin SSOP W Rail |

| 74VHC161284MEA_Q | 功能描述:總線收發(fā)器 IEEE 16284 Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

| 74VHC161284MEAX | 功能描述:總線收發(fā)器 IEEE 16284 Trans RoHS:否 制造商:Fairchild Semiconductor 邏輯類型:CMOS 邏輯系列:74VCX 每芯片的通道數(shù)量:16 輸入電平:CMOS 輸出電平:CMOS 輸出類型:3-State 高電平輸出電流:- 24 mA 低電平輸出電流:24 mA 傳播延遲時間:6.2 ns 電源電壓-最大:2.7 V, 3.6 V 電源電壓-最小:1.65 V, 2.3 V 最大工作溫度:+ 85 C 封裝 / 箱體:TSSOP-48 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復。