- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360498 > 74LVC273PWDH (NXP SEMICONDUCTORS) Quadruple 2-Input Positive-OR Gates 14-SOIC -40 to 85 PDF資料下載

參數(shù)資料

| 型號: | 74LVC273PWDH |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Quadruple 2-Input Positive-OR Gates 14-SOIC -40 to 85 |

| 中文描述: | LVC/LCX/Z SERIES, POSITIVE EDGE TRIGGERED D FLIP-FLOP, TRUE OUTPUT, PDSO20 |

| 文件頁數(shù): | 2/10頁 |

| 文件大小: | 95K |

| 代理商: | 74LVC273PWDH |

Philips Semiconductors

Product specification

74LVC273

Octal D-type flip-flop with reset; positive-edge trigger

2

1998 May 20

853-2064 19419

FEATURES

Wide supply voltage range of 1.2V to 3.6V

Conforms to JEDEC standard 8-1A

Inputs accept voltages up to 5.5V

CMOS low power consumption

Direct interface with TTL levels

Output drive capability 50

transmission lines @ 85

°

C

DESCRIPTION

The 74LVC273 is a low-voltage Si-gate CMOS device, superior to

most advanced CMOS compatible TTL families.

The 74LVC273 has eight edge-triggered , D-type flip-flops with

individual D inputs and Q outputs. The common clock (CP) and

master reset (MR) inputs load and reset (clear) all flip-flops

simultaneously. The state of each D input, one set-up time before

the LOW-to-HIGH clock transition, is transferred to the

corresponding output (Qn) of the flip-flop.

All outputs will be forced LOW independently of clock or data inputs

by a LOW voltage level on the MR input.

The device is useful for applications where the true output only is

required and the clock and master reset are common to all storage

elements.

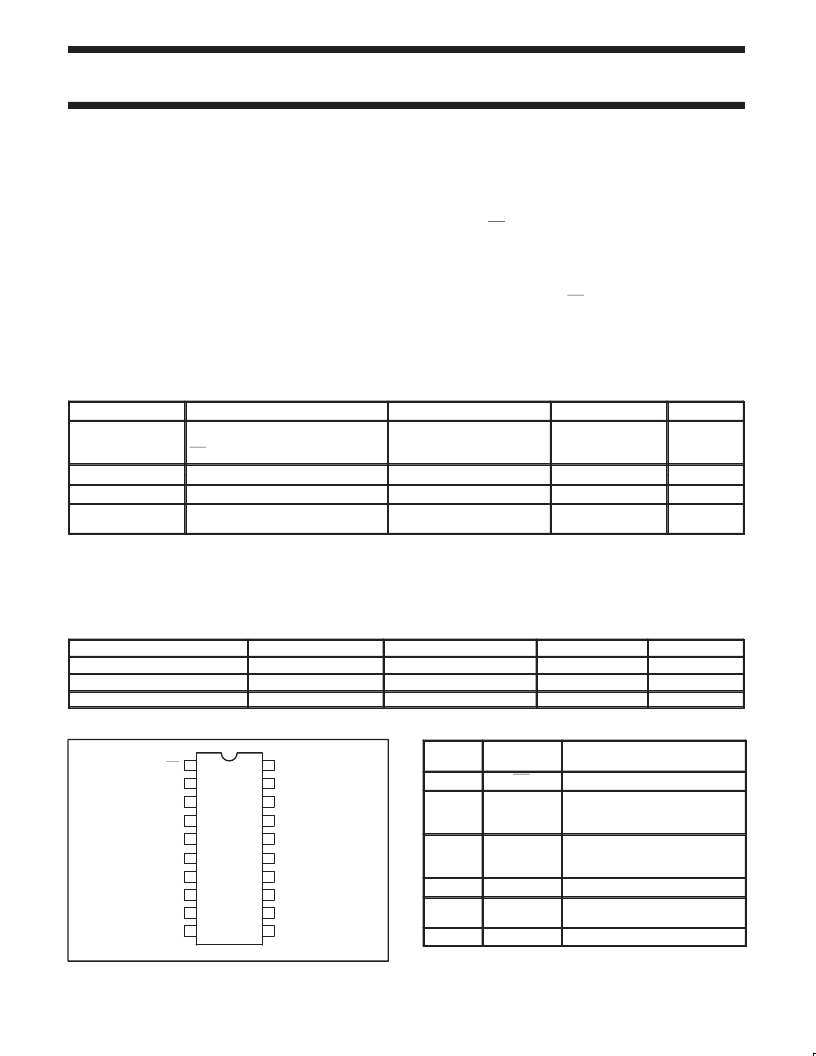

QUICK REFERENCE DATA

GND = 0V; T

amb

= 25

°

C; t

r

=t

f

SYMBOL

2.5 ns

PARAMETER

CONDITIONS

TYPICAL

UNIT

t

PHL

/t

PLH

Propagation delay

CP to Qn;

MR to Q

n

C

L

= 50pF

V

CC

= 3.3V

6.0

6.0

ns

f

max

C

I

Maximum clock frequency

230

MHz

Input capacitance

5.0

pF

C

PD

Power dissipation

capacitance per flip-flop

V

I

= GND to V

CC1

22

pF

NOTE:

1

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W)

P

D

= C

PD

V

CC2

x f

i

(C

L

f

i

= input frequency in MHz; C

L

= output load capacity in pF;

f

o

= output frequency in MHz; V

CC

= supply voltage in V;

(C

L

V

CC2

f

o

) = sum of the outputs.

V

CC2

f

o

) where:

ORDERING INFORMATION

PACKAGES

20-Pin Plastic SO

20-Pin Plastic SSOP Type II

20-Pin Plastic TSSOP Type I

TEMPERATURE RANGE

–40

°

C to +85

°

C

–40

°

C to +85

°

C

–40

°

C to +85

°

C

OUTSIDE NORTH AMERICA

74LVC273 D

74LVC273 DB

74LVC273 PW

NORTH AMERICA

74LVC273 D

74LVC273 DB

74LVC273PW DH

DWG NUMBER

SOT163-1

SOT339-1

SOT360-1

PIN CONFIGURATION

14

13

12

11

10

9

8

7

6

5

4

3

2

1

GND

V

CC

15

16

17

18

19

20

MR

Q0

D0

D1

Q1

Q2

D2

D3

Q3

Q7

D7

D6

Q6

Q5

D5

D4

Q4

CP

SY00051

PIN DESCRIPTION

PIN

NUMBER

SYMBOL

FUNCTION

1

MR

Master reset input (active LOW)

2, 5, 6,

9, 12, 15,

16, 19

Q0 – Q7

Flip-flop outputs

3, 4, 7,

8, 13, 14,

17, 18

D0 – D7

Data inputs

10

GND

Ground (0V)

11

CP

Clock input (LOW-to-HIGH,

edge-triggered)

20

V

CC

Positive power supply

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LVC27 | Quadruple 2-Input Positive-OR Gates 14-SSOP -40 to 85 |

| 74LVC27PWDH | Quadruple 2-Input Positive-OR Gates 14-SOIC -40 to 85 |

| 74LVC2952APWDH | Octal registered tranceiver with 5-volt tolerant inputs/ouputs 3-State |

| 74LVC2952A | Quadruple 2-Input Positive-OR Gates 14-SOIC -40 to 85 |

| 74LVC2G241 | CABLE 37 COND 100FT SHIELD FLAT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LVC273PW-Q100J | 制造商:NXP Semiconductors 功能描述:74LVC273PW-Q100/TSSOP20/REEL13 - Tape and Reel 制造商:NXP Semiconductors 功能描述:IC D-TYPE POS TRG SNGL 20TSSOP |

| 74LVC27BQ | 制造商:NXP Semiconductors 功能描述:IC 3 INPUT NOR GATE DHVQFN14 |

| 74LVC27BQ,115 | 功能描述:邏輯門 3.3V TRIPLE 3-INPUT RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| 74LVC27BQ-G | 功能描述:邏輯門 3.3V TRIPLE 3-INPUT NOR GATE RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

| 74LVC27D | 功能描述:邏輯門 TRIPLE 3-IN NOR GATE RoHS:否 制造商:Texas Instruments 產(chǎn)品:OR 邏輯系列:LVC 柵極數(shù)量:2 線路數(shù)量(輸入/輸出):2 / 1 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 傳播延遲時間:3.8 ns 電源電壓-最大:5.5 V 電源電壓-最小:1.65 V 最大工作溫度:+ 125 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:DCU-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。