- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360497 > 74LVC10 (NXP Semiconductors N.V.) Triple 3-input NAND gate PDF資料下載

參數(shù)資料

| 型號: | 74LVC10 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Triple 3-input NAND gate |

| 中文描述: | 三3輸入與非門 |

| 文件頁數(shù): | 4/8頁 |

| 文件大?。?/td> | 84K |

| 代理商: | 74LVC10 |

Philips Semiconductors

Product specification

74LVC10A

Triple 3-input NAND gate

1998 Apr 28

4

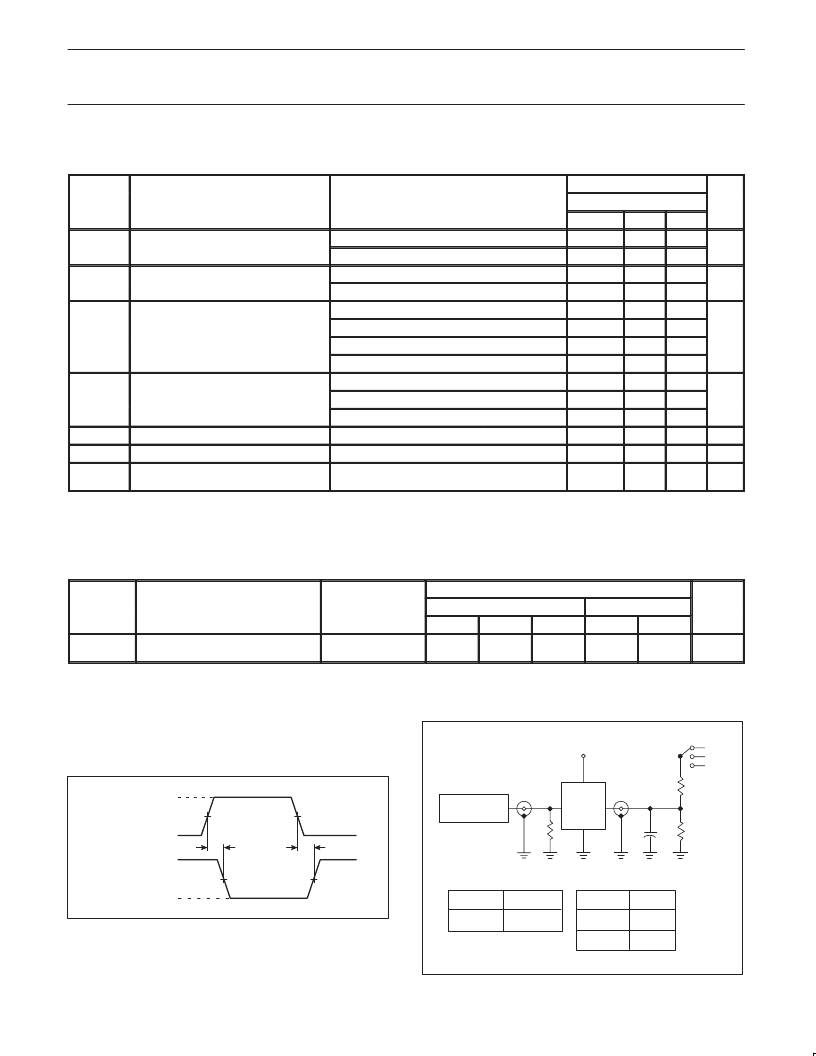

DC ELECTRICAL CHARACTERISTICS

Over recommended operating conditions. Voltages are referenced to GND (ground = 0V).

LIMITS

SYMBOL

PARAMETER

TEST CONDITIONS

Temp = -40

°

C to +85

°

C

MIN

TYP

1

V

CC

2.0

UNIT

MAX

V

IH

HIGH level Input voltage

V

CC

= 1.2V

V

CC

= 2.7 to 3.6V

V

CC

= 1.2V

V

CC

= 2.7 to 3.6V

V

CC

= 2.7V; V

I

= V

IH

or V

IL

; I

O

= –12mA

V

CC

= 3.0V; V

I

= V

IH

or V

IL

; I

O

= –100

μ

A

V

CC

= 3.0V; V

I

= V

IH

or V

IL;

I

O

= –12mA

V

CC

= 3.0V; V

I

= V

IH

or V

IL;

I

O

= –24mA

V

CC

= 2.7V; V

I

= V

IH

or V

IL

; I

O

= 12mA

V

CC

= 3.0V; V

I

= V

IH

or V

IL

; I

O

= 100

μ

A

V

CC

= 3.0V; V

I

= V

IH

or V

IL;

I

O

= 24mA

V

CC

= 3.6V; V

I

= 5.5V or GND

V

CC

= 3.6V; V

I

= V

CC

or GND; I

O

= 0

V

V

IL

LOW level Input voltage

GND

V

0.8

V

CC

V

CC

V

CC

V

CC

0.5

V

OH

HIGH level output voltage

0.2

V

CC

V

0.6

1.0

0.40

V

OL

LOW level output voltage

0.20

V

0.55

I

I

Input leakage current

0.1

5

μ

A

μ

A

I

CC

Quiescent supply current

0.1

10

I

CC

Additional quiescent supply current per

input pin

V

CC

= 2.7V to 3.6V; V

I

= V

CC

–0.6V; I

O

= 0

5

500

μ

A

NOTE:

1. All typical values are at V

CC

= 3.3V and T

amb

= 25

°

C.

AC CHARACTERISTICS

GND = 0 V; t

r

= t

f

2.5 ns; C

L

= 50 pF

LIMITS

SYMBOL

PARAMETER

WAVEFORM

V

CC

= 3.3V

±

0.3V

TYP

1

V

CC

= 2.7V

MIN

UNIT

MIN

MAX

MAX

t

PHL

/

t

PLH

Propagation delay

nA, nB, nC to nY

Figures 1, 2

1.5

3.9

5.7

1.5

6.7

ns

NOTE:

1. These typical values are at V

CC

= 3.3V and T

amb

= 25

°

C.

AC WAVEFORMS

V

M

= 1.5 V at V

CC

V

M

= 0.5 V

CC

at V

CC

< 2.7 V

V

OL

and V

OH

are the typical output voltage drop that occur with the

output load.

2.7 V

SV00420

VM

nA, nB, nC

INPUT

nY OUTPUT

VM

tPLH

tPHL

GND

VI

VOL

VOH

Figure 1. Input (nA, nB, nC) to output (nY)

propagation delays.

TEST CIRCUIT

SWITCH POSITION

PULSE

GENERATOR

R

T

V

I

D.U.T.

V

O

C

L

V

CC

500

Open

GND

S

1

V

CC

V

I

< 2.7V

V

CC

TEST

S

1

t

PLH/

t

PHL

Open

2.7V

2.7–3.6V

50pF

500

2 * V

CC

SV00903

Figure 2. Load circuitry for switching times.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LVC10DB | Triple 3-input NAND gate |

| 74LVC10PW | Triple 3-input NAND gate |

| 74LVC10PWDH | Triple 3-input NAND gate |

| 74LVC10D | Data Selectors/Multiplexers With 3-State Outputs 16-SOIC -40 to 85 |

| 74LVC11 | Data Selectors/Multiplexers With 3-State Outputs 16-SSOP -40 to 85 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LVC109 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Dual JK flip-flop with set and reset; positive-edge trigger |

| 74LVC109ASO | 制造商:Integrated Device Technology Inc 功能描述:74LVC109ASO - Bulk |

| 74LVC109AXTDC | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Integrated Device Technology Inc 功能描述: |

| 74LVC109AXTPY | 制造商:Rochester Electronics LLC 功能描述:- Bulk 制造商:Integrated Device Technology Inc 功能描述: |

| 74LVC109D | 制造商:NXP Semiconductors 功能描述:Flip Flop JK# -Type Pos-Edge 2-Element 16-Pin SO |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。