- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄370132 > 74LS640 (Motorola, Inc.) OCTAL BUS TRANSCEIVERS PDF資料下載

參數(shù)資料

| 型號: | 74LS640 |

| 廠商: | Motorola, Inc. |

| 英文描述: | OCTAL BUS TRANSCEIVERS |

| 中文描述: | 八進制總線收發(fā)器 |

| 文件頁數(shù): | 1/3頁 |

| 文件大小: | 83K |

| 代理商: | 74LS640 |

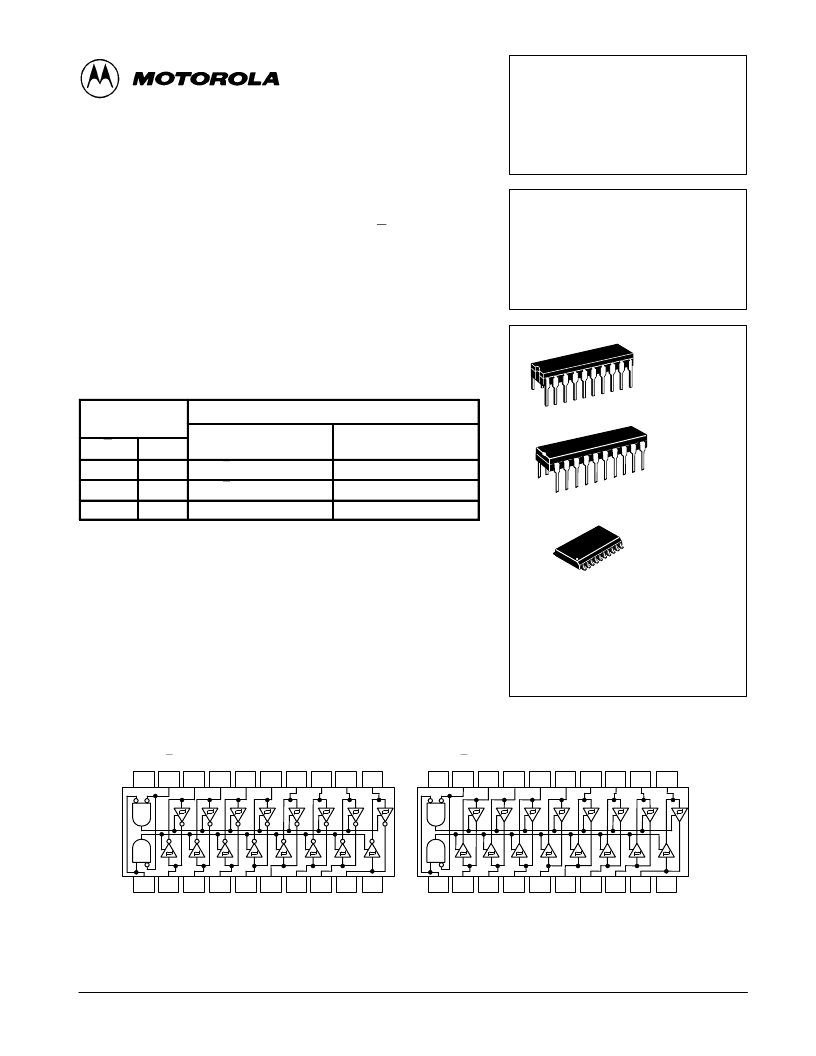

CONNECTION DIAGRAMS DIP

(TOP VIEW)

18

17

16

15

14

13

1

2

3

4

A3

5

6

7

A6

20

19

8

A7

VCC

DIR

B1

B2

B3

B5

B4

B6

A1

A2

A4

A5

9

10

GND

A8

12

11

B7

B8

18

17

16

15

14

13

1

2

3

4

A3

5

6

7

A6

20

19

8

A7

VCC

DIR

B1

B2

B3

B5

B4

B6

A1

A2

A4

A5

9

10

GND

A8

12

11

B7

B8

SN54/74LS640

SN54/74LS642

SN54/74LS641

SN54/74LS645

ENABLE

G

ENABLE

G

5-1

FAST AND LS TTL DATA

OCTAL BUS TRANSCEIVERS

These octal bus transceivers are designed for asynchronous two-way

communication between data buses. Control function implementation

minimizes external timing requirements. These circuits allow data transmis-

sion from the A bus to B or from the B bus to A bus depending upon the logic

level of the direction control (DIR) input. Enable input (G) can disable the

device so that the buses are effectively isolated.

DEVICE

LS640

LS641

LS642

LS645

OUTPUT

3-State

Open-Collector

Open-Collector

3-State

LOGIC

Inverting

True

Inverting

True

FUNCTION TABLE

CONTROL

INPUTS

OPERATION

LS640

LS642

LS641

LS645

G

DIR

L

L

B data to A bus

B data to A bus

L

H

A data to B bus

A data to B bus

H

X

Isolation

Isolation

H = HIGH Level, L = LOW Level, X = Irrelevant

SN54/74LS640

SN54/74LS641

SN54/74LS642

SN54/74LS645

OCTAL BUS TRANSCEIVERS

LOW POWER SCHOTTKY

ORDERING INFORMATION

SN54LSXXXJ

SN74LSXXXN

SN74LSXXXDW SOIC

Ceramic

Plastic

20

1

J SUFFIX

CERAMIC

CASE 732-03

20

1

N SUFFIX

PLASTIC

CASE 738-03

20

1

DW SUFFIX

SOIC

CASE 751D-03

相關PDF資料 |

PDF描述 |

|---|---|

| 74LS77 | 4-BIT D LATCH LOW POWER SCHOTTKY |

| 74LS83 | 4-BIT BINARY FULL ADDER WITH FAST CARRY |

| 74LS83 | 4-Bit Binary Adder with Fast Carry |

| 74LS85 | LOW POWER SCHOTTKY |

| 74LS85 | 4-Bit Magnitude Comparator |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| 74LS640N | 制造商:Motorola 功能描述:74LS640 MOT'82 NXC2A |

| 74LS641-1N | 制造商:NXP Semiconductors 功能描述: |

| 74LS641N | 制造商:SNT 功能描述: |

| 74LS645 | 制造商:MOTOROLA 制造商全稱:Motorola, Inc 功能描述:OCTAL BUS TRANSCEIVERS |

| 74LS645-1N | 制造商:Advanced Micro Devices 功能描述: 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。