- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375080 > 74LS390 (Fairchild Semiconductor Corporation) Dual 4-Bit Decade Counter PDF資料下載

參數(shù)資料

| 型號(hào): | 74LS390 |

| 廠商: | Fairchild Semiconductor Corporation |

| 元件分類: | 通用總線功能 |

| 英文描述: | Dual 4-Bit Decade Counter |

| 中文描述: | 雙4位十進(jìn)制計(jì)數(shù)器 |

| 文件頁(yè)數(shù): | 1/6頁(yè) |

| 文件大?。?/td> | 58K |

| 代理商: | 74LS390 |

2000 Fairchild Semiconductor Corporation

DS006433

www.fairchildsemi.com

August 1986

Revised March 2000

D

DM74LS390

Dual 4-Bit Decade Counter

General Description

Each of these monolithic circuits contains eight master-

slave flip-flops and additional gating to implement two indi-

vidual four-bit counters in a single package. The

DM74LS390 incorporates dual divide-by-two and divide-

by-five counters, which can be used to implement cycle

lengths equal to any whole and/or cumulative multiples of 2

and/or 5 up to divide-by-100. When connected as a bi-qui-

nary counter, the separate divide-by-two circuit can be

used to provide symmetry (a square wave) at the final out-

put stage. The DM74LS390 has parallel outputs from each

counter stage so that any submultiple of the input count fre-

quency is available for system-timing signals.

Features

I

Dual version of the popular DM74LS90

I

DM74LS390...individual clocks for A and B flip-flops

provide dual

÷

2 and

÷

5 counters

I

Direct clear for each 4-bit counter

I

Dual 4-bit version can significantly improve system den-

sities by reducing counter package count by 50%

I

Typical maximum count frequency...35 MHz

I

Buffered outputs reduce possibility of collector commu-

tation

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

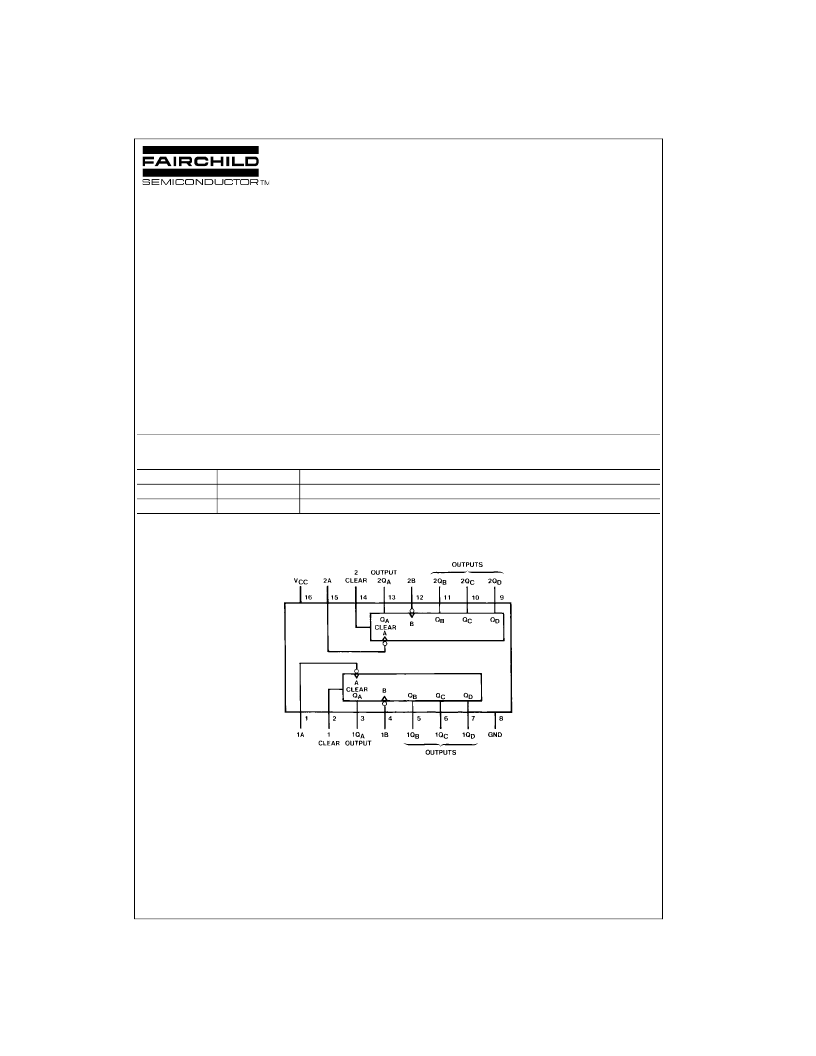

Connection Diagram

Order Number

DM74LS390M

DM74LS390N

Package Number

M16A

N16E

Package Description

16-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-012, 0.150 Narrow

16-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74LVQ151SC | Low Voltage 8-Input Multiplexer |

| 74LVQ151 | Low Voltage 8-Input Multiplexer |

| 74LVQ151SJ | CAP .1UF 1250V METAL POLYPRO |

| 74LVQ244 | Low Voltage Octal Buffer/Line Driver with 3-STATE Outputs |

| 74LVQ244QSC | 8KB FLASH; 512 RAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74LS393 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:DUAL 4-BIT DECADE AND BINARY COUNTERS |

| 74LS393DC | 制造商:Texas Instruments 功能描述: |

| 74LS393N | 制造商:Semiconductors 功能描述: |

| 74LS393PC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 74LS393PCQR | 制造商:Texas Instruments 功能描述: |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。