- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360463 > 74HC7597 (NXP Semiconductors N.V.) 8-bit shift register with input latches PDF資料下載

參數(shù)資料

| 型號: | 74HC7597 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | 8-bit shift register with input latches |

| 中文描述: | 8位輸入鎖存移位寄存器 |

| 文件頁數(shù): | 2/12頁 |

| 文件大小: | 90K |

| 代理商: | 74HC7597 |

December 1990

2

Philips Semiconductors

Product specification

8-bit shift register with input latches

74HC/HCT7597

FEATURES

8-bit parallel input latches

Shift register has direct overriding load and clear

Output capability: standard

I

CC

category: MSI

GENERAL DESCRIPTION

The 74HC/HCT7597 are high-speed Si-gate CMOS

devices and are pin compatible with low power Schottky

TTL (LSTTL). They are specified in compliance with

JEDEC standard no. 7A.

The 74HC/HCT7597 both consist of an 8-bit storage latch

feeding a parallel-in, serial-out 8-bit shift register.

When LE is LOW, data at the D

n

inputs enter the latches.

In this condition the latches are transparent, i.e. a latch

output will change state each time its corresponding

D-input changes.

When LE is HIGH the latches store the information that

was present at the D-inputs, a set-up time preceding the

LOW-to-HIGH transition of LE.

The shift register has a positive edge-triggered clock,

direct load (from storage) and clear inputs.

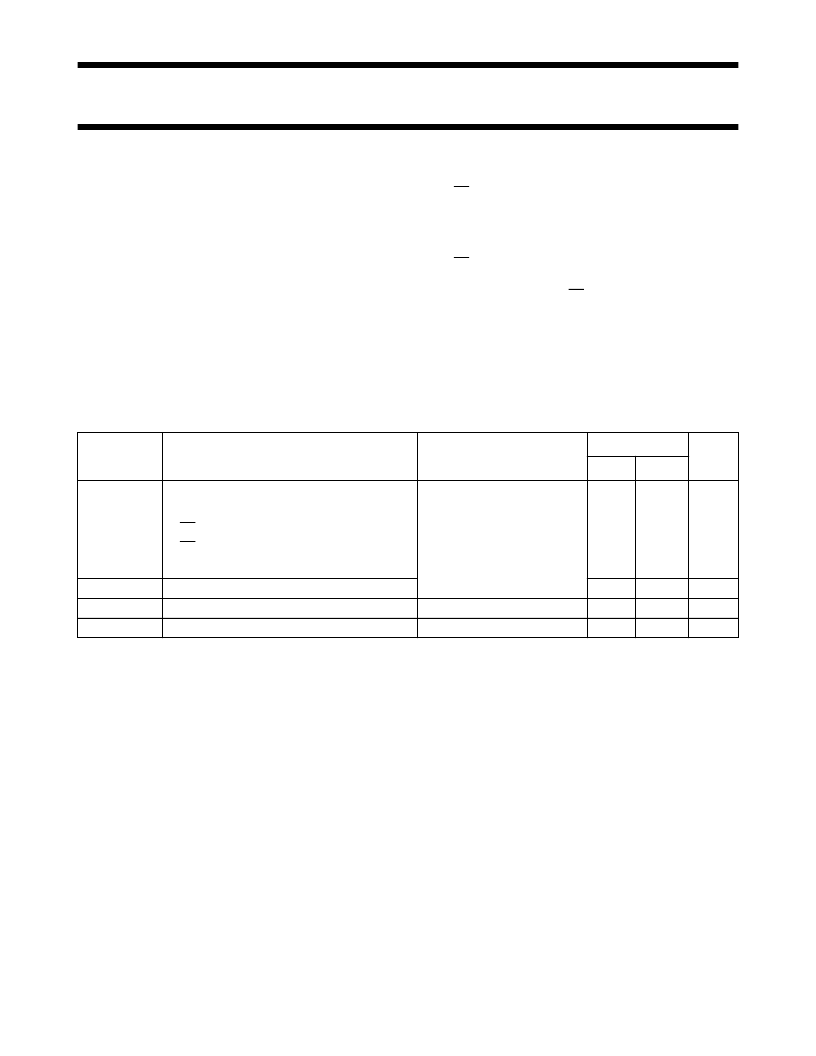

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

°

C; t

r

= t

f

= 6 ns

Notes

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W):

P

D

= C

PD

×

V

CC2

×

f

i

+ ∑

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz; f

o

= output frequency in MHz

∑

(C

L

×

V

CC2

×

f

o

) = sum of outputs

C

L

= output load capacitance in pF; V

CC

= supply voltage in V

For HC the condition is V

I

= GND to V

CC

; for HCT the condition is V

I

= GND to V

CC

1.5 V

2.

ORDERING INFORMATION

See

“74HC/HCT/HCU/HCMOS Logic Package Information”

.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

HC

HCT

t

PHL

/ t

PLH

propagation delay

SH

CP

to Q

LE to Q

PL to Q

D

7

to Q

maximum clock frequency SH

CP

input capacitance

power dissipation capacitance per package

C

L

= 15 pF; V

CC

= 5 V

15

22

20

20

99

3.5

29

17

27

23

24

79

3.5

30

ns

ns

ns

ns

MHz

pF

pF

f

max

C

I

C

PD

notes 1, 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74HCT7597 | Dual 4-Input Positive-AND Gates 14-SOIC -40 to 85 |

| 74HC7731 | Quad 64-bit static shift register |

| 74HCT7731 | Dual 4-Input Positive-AND Gates 14-PDIP -40 to 85 |

| 74HC85 | 4-bit magnitude comparator |

| 74HCT85 | 4-bit magnitude comparator(8位相同比較器) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74HC75D | 功能描述:閉鎖 QUAD BISTABLE LATCH RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74HC75D,652 | 功能描述:閉鎖 QUAD BISTABLE LATCH RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74HC75D,653 | 功能描述:閉鎖 QUAD BISTABLE LATCH RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74HC75D | 制造商:NXP Semiconductors 功能描述:IC 74HC CMOS SMD 74HC75 SOIC16 |

| 74HC75D652 | 制造商:NXP Semiconductors 功能描述:IC QUAD BISTABLE TRANSPARENT LATCH SOI |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。