- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360457 > 74HC164 (System Logic Semiconductor Co., Ltd.) 8-Bit Serial-Input/Parallel-Output8-Bit Serial-Input/Parallel-Output Shift Register PDF資料下載

參數(shù)資料

| 型號: | 74HC164 |

| 廠商: | System Logic Semiconductor Co., Ltd. |

| 英文描述: | 8-Bit Serial-Input/Parallel-Output8-Bit Serial-Input/Parallel-Output Shift Register |

| 中文描述: | 8位Serial-Input/Parallel-Output8-Bit Serial-Input/Parallel-Output移位寄存器 |

| 文件頁數(shù): | 14/24頁 |

| 文件大小: | 131K |

| 代理商: | 74HC164 |

9397 750 14693

Koninklijke Philips Electronics N.V. 2005. All rights reserved.

Product data sheet

Rev. 03 — 4 April 2005

14 of 24

Philips Semiconductors

74HC164; 74HCT164

8-bit serial-in, parallel-out shift register

t

W

clock pulse width;

HIGH or LOW

master reset pulse width;

LOW

removal time MR to CP

V

CC

= 4.5 V;

see

Figure 7

V

CC

= 4.5 V;

see

Figure 8

V

CC

= 4.5 V;

see

Figure 8

V

CC

= 4.5 V;

see

Figure 9

V

CC

= 4.5 V;

see

Figure 9

V

CC

= 4.5 V;

see

Figure 7

27

-

-

ns

27

-

-

ns

t

rem

24

-

-

ns

t

su

set-up time

DSA and DSB to CP

hold time DSA and DSB

to CP

maximum clock pulse

frequency

18

-

-

ns

t

h

4

-

-

ns

f

max

18

-

-

MHz

(1) 74HC164: V

M

= 50 %; V

I

= GND to V

CC

.

74HCT164: V

M

= 1.3 V; V

I

= GND to 3 V.

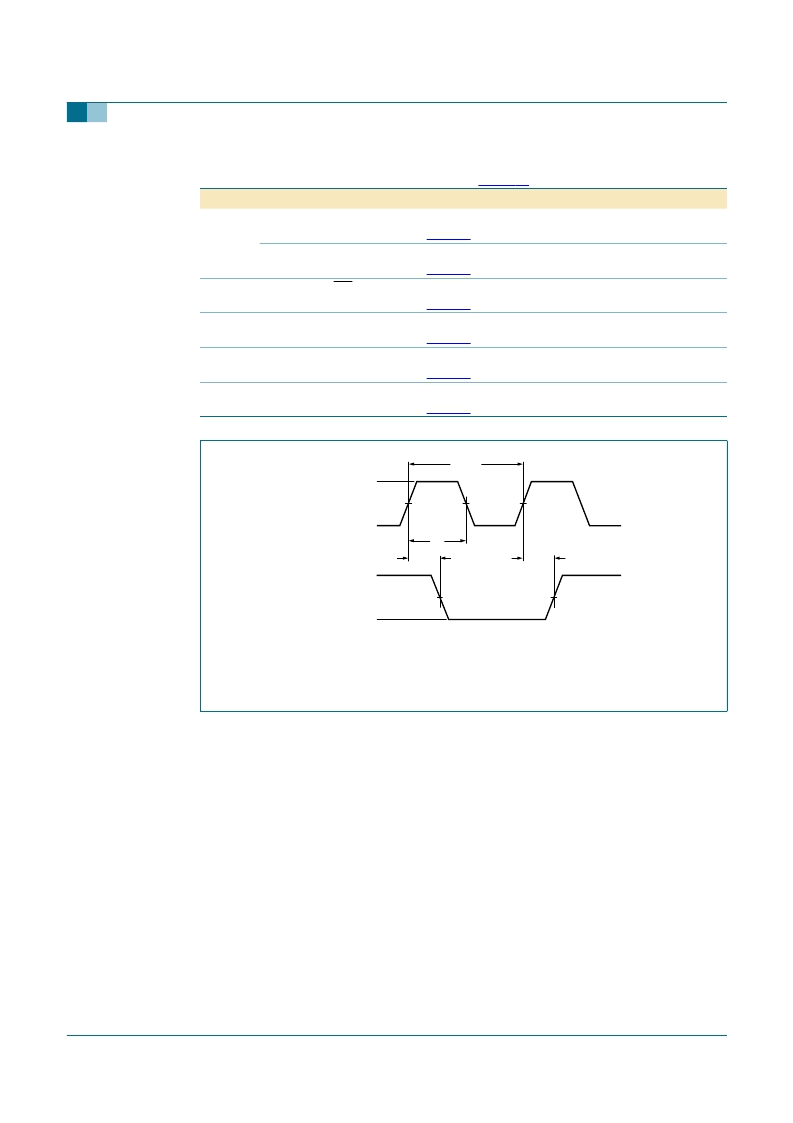

Fig 7.

Waveforms showing the clock (CP) to output (Qn) propagation delays, the clock

pulse width, the output transition times and the maximum clock frequency

Table 10:

GND = 0 V; t

r

= t

f

= 6 ns; C

L

= 50 pF; test circuit see

Figure 10

; unless otherwise specified

Symbol

Parameter

Conditions

Dynamic characteristics for 74HCT164

…continued

Min

Typ

Max

Unit

001aac426

CP input

Qn output

t

PHL

t

PLH

t

W

V

OH

V

I

GND

V

OL

V

M

V

M

1/f

max

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。