- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360456 > 74HC00 (NXP Semiconductors N.V.) Quad 2-input NAND gate PDF資料下載

參數(shù)資料

| 型號(hào): | 74HC00 |

| 廠商: | NXP Semiconductors N.V. |

| 英文描述: | Quad 2-input NAND gate |

| 中文描述: | 四2輸入與非門 |

| 文件頁數(shù): | 2/17頁 |

| 文件大小: | 98K |

| 代理商: | 74HC00 |

2003 Jun 30

2

Philips Semiconductors

Product specification

Quad 2-input NAND gate

74HC00; 74HCT00

FEATURES

Complies with JEDEC standard no. 8-1A

ESD protection:

HBM EIA/JESD22-A114-A exceeds 2000 V

MM EIA/JESD22-A115-A exceeds 200 V

Specified from

40 to +85

°

C and

40 to +125

°

C.

DESCRIPTION

The 74HC00/74HCT00 are high-speed Si-gate CMOS

devices and are pin compatible with low power Schottky

TTL (LSTTL). They are specified in compliance with

JEDEC standard no. 7A.

The 74HC00/74HCT00 provide the 2-input NAND

function.

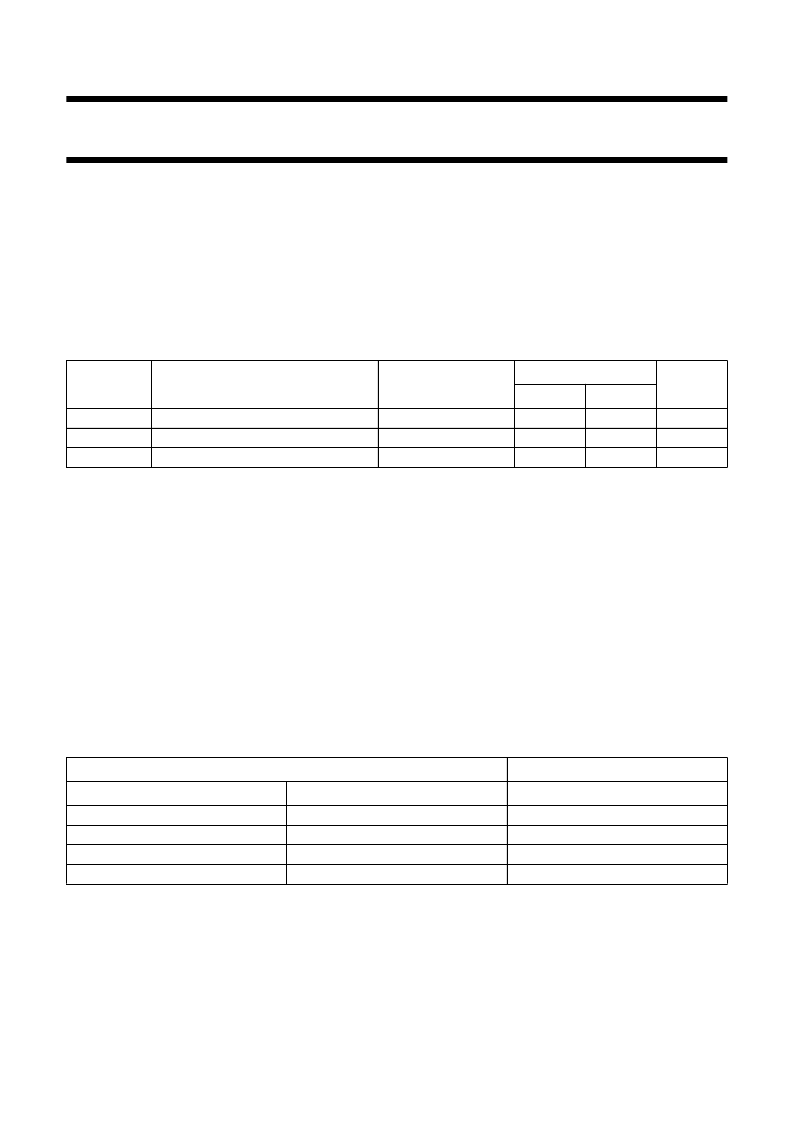

QUICK REFERENCE DATA

GND = 0 V; T

amb

= 25

°

C; t

r

= t

f

= 6 ns.

Notes

1.

C

PD

is used to determine the dynamic power dissipation (P

D

in

μ

W).

P

D

= C

PD

×

V

CC2

×

f

i

×

N +

Σ

(C

L

×

V

CC2

×

f

o

) where:

f

i

= input frequency in MHz;

f

o

= output frequency in MHz;

C

L

= output load capacitance in pF;

V

CC

= supply voltage in Volts;

N = total load switching outputs;

Σ

(C

L

×

V

CC2

×

f

o

) = sum of the outputs.

For 74HC00 the condition is V

I

= GND to V

CC

.

For 74HCT00 the condition is V

I

= GND to V

CC

1.5 V.

2.

FUNCTION TABLE

See note 1.

Note

1.

H = HIGH voltage level;

L = LOW voltage level.

SYMBOL

PARAMETER

CONDITIONS

TYPICAL

UNIT

74HC00

74HCT00

t

PHL

/t

PLH

C

I

C

PD

propagation delay nA, nB to nY

input capacitance

power dissipation capacitance per gate notes 1 and 2

C

L

= 15 pF; V

CC

= 5 V

7

3.5

22

10

3.5

22

ns

pF

pF

INPUT

OUTPUT

nA

nB

nY

L

L

H

H

L

H

L

H

H

H

H

L

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74HCT00 | Quad 2-input NAND gate |

| 74HC02 | Quad 2-input NOR gate |

| 74HCT02 | Quad 2-input NOR gate |

| 74HC03 | Quad 2-input NAND gate |

| 74HCT03 | Quad 2-input NAND gate |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74HC002 | 制造商:NXP Semiconductors 功能描述: |

| 74HC00A | 制造商:Toshiba America Electronic Components 功能描述: |

| 74HC00AD | 制造商: 功能描述: 制造商:Motorola Inc 功能描述: 制造商:undefined 功能描述: |

| 74HC00AP | 制造商:Toshiba America Electronic Components 功能描述: |

| 74HC00BQ | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Quad 2-input NAND gate |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。