- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360437 > 74F533PC (FAIRCHILD SEMICONDUCTOR CORP) Octal Transparent Latch with 3-STATE Outputs PDF資料下載

參數(shù)資料

| 型號(hào): | 74F533PC |

| 廠商: | FAIRCHILD SEMICONDUCTOR CORP |

| 元件分類: | 通用總線功能 |

| 英文描述: | Octal Transparent Latch with 3-STATE Outputs |

| 中文描述: | F/FAST SERIES, 8-BIT DRIVER, INVERTED OUTPUT, PDIP20 |

| 封裝: | 0.300 INCH, PLASTIC, MS-001, DIP-20 |

| 文件頁數(shù): | 6/12頁 |

| 文件大小: | 97K |

| 代理商: | 74F533PC |

Philips Semiconductors

Product specification

74F533,* 74F534

Latch/flip-flop

1999 Jan 08

6

* Discontinued part. Please see the Discontinued Products List.

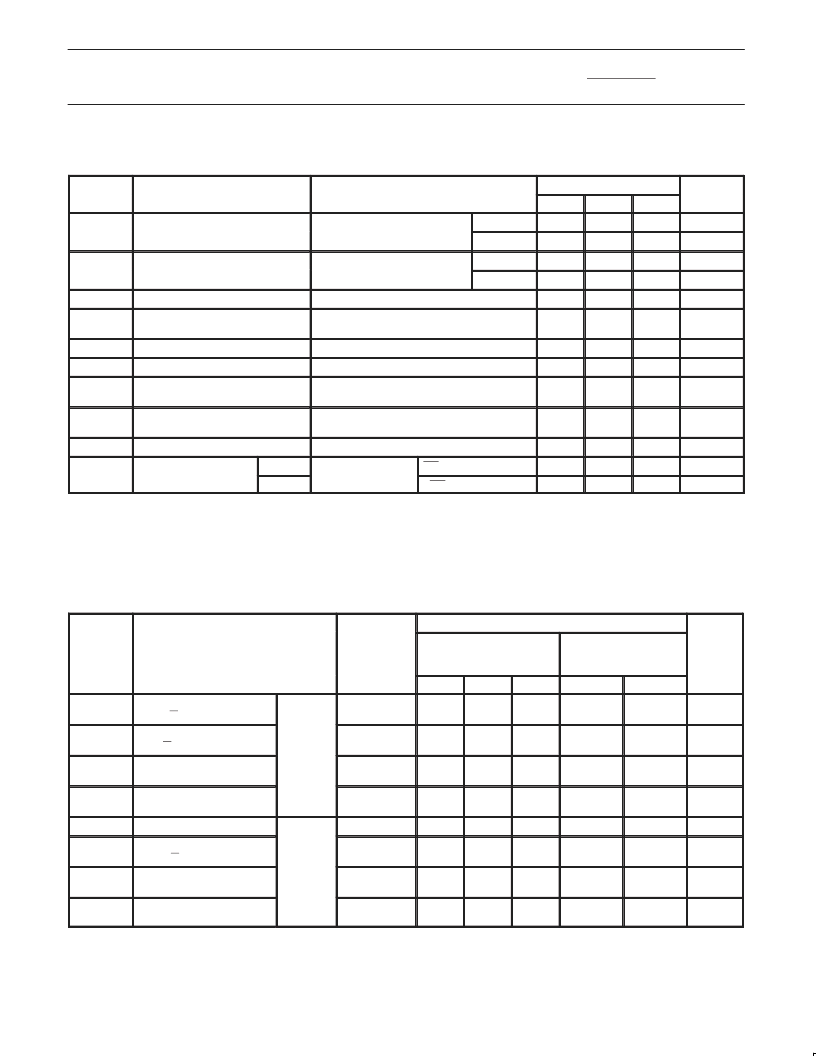

DC ELECTRICAL CHARACTERISTICS

(Over recommended operating free-air temperature range unless otherwise noted.)

SYMBOL

PARAMETER

TEST CONDITIONS

1

LIMITS

TYP

2

UNIT

MIN

MAX

V

OH

High level output voltage

High-level output voltage

= MIN, V

= MAX,

V

CC

MIN, V

IL

MAX,

V

IH

= MIN, I

OH

= MAX

±

10%V

CC

±

5%V

CC

±

10%V

CC

±

5%V

CC

2.4

V

2.7

3.3

V

V

OL

Low level output voltage

Low-level output voltage

CC

= MIN, V

IL

= MAX,

V

MIN, V

MAX,

V

IH

= MIN, I

OL

= MAX

0.35

0.50

V

0.35

0.50

V

V

IK

Input clamp voltage

V

CC

= MIN, I

I

= I

IK

–0.73

–1.2

V

I

I

Input current at

maximum input voltage

V

CC

= MAX, V

I

= 7.0V

100

μ

A

I

IH

I

IL

High-level input current

V

CC

= MAX, V

I

= 2.7V

V

CC

= MAX, V

I

= 0.5V

20

μ

A

Low-level input current

–0.6

mA

I

OZH

Off-state output current,

High-level voltage applied

V

CC

= MAX, V

O

= 2.7V

50

μ

A

I

OZL

Off-state output current,

Low-level voltage applied

Short-circuit output current

3

V

CC

= MAX, V

O

= 0.5V

–50

μ

A

I

OS

V

CC

= MAX

–60

–150

mA

I

CC

Supply current (total)

74F533

V

CC

= MAX

OE=4.5V, Dn=E=GND

41

61

mA

74F534

OE=4.5V, Dn=GND

51

86

mA

NOTES:

1. For conditions shown as MIN or MAX, use the appropriate value specified under recommended operating conditions for the applicable type.

2. All typical values are at V

CC

= 5V, T

amb

= 25

°

C.

3. Not more than one output should be shorted at a time. For testing I

OS

, the use of high-speed test apparatus and/or sample-and-hold

techniques are preferable in order to minimize internal heating and more accurately reflect operational values. Otherwise, prolonged shorting

of a High output may raise the chip temperature well above normal and thereby cause invalid readings in other parameter tests. In any

sequence of parameter tests, I

OS

tests should be performed last.

AC ELECTRICAL CHARACTERISTICS

LIMITS

SYMBOL

PARAMETER

TEST

CONDITIONS

T

amb

= +25

°

C

V

= +5V

C

L

= 50pF, R

L

= 500

MIN

TYP

T

amb

= 0

°

C to +70

°

C

V

= +5V

±

10%

C

L

= 50pF, R

L

= 500

MIN

UNIT

MAX

MAX

t

PLH

t

PHL

t

PLH

t

PHL

t

PZH

t

PZL

t

PHZ

t

PLZ

f

MAX

t

PLH

t

PHL

t

PZH

t

PZL

t

PHZ

t

PLZ

Propagation delay

Dn to Qn

Waveform 2

4.0

3.0

6.0

4.5

8.5

7.0

4.0

3.0

9.5

8.0

ns

Propagation delay

E to Qn

74F533

Waveform 3

5.0

3.0

6.5

4.5

9.5

7.0

5.0

3.0

10.0

8.0

ns

Output Enable time

to High or Low level

Waveform 6

Waveform 7

2.0

2.0

4.5

5.0

7.0

7.0

2.0

2.0

8.0

8.0

ns

Output Disable time

from High or Low level

Waveform 6

Waveform 7

2.0

2.0

3.5

3.0

6.0

5.5

2.0

2.0

7.0

6.5

ns

Maximum Clock frequency

Waveform 1

150

165

135

MHz

Propagation delay

CP to Qn

Waveform 1

3.0

3.0

4.5

4.5

7.0

7.0

2.5

2.5

7.5

7.5

ns

Output Enable time

to High or Low level

74F534

Waveform 6

Waveform 7

2.0

2.0

4.5

5.0

7.5

7.5

2.0

2.0

8.5

8.5

ns

Output Disable time

from High or Low level

Waveform 6

Waveform 7

2.0

2.0

3.5

3.5

6.5

5.5

2.0

2.0

7.5

6.5

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F533SC | Octal Transparent Latch with 3-STATE Outputs |

| 74F533SJ | Octal Transparent Latch with 3-STATE Outputs |

| 74F534 | Octal D-Type Flip-Flop with 3-STATE Outputs |

| 74F534PC | Octal D-Type Flip-Flop with 3-STATE Outputs |

| 74F534SC | Octal D-Type Flip-Flop with 3-STATE Outputs |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F533PC_Q | 功能描述:閉鎖 Octal Trans Latch RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| 74F533PCQB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Transparent Latch with TRI-STATE Outputs |

| 74F533PCX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Transparent Latch with TRI-STATE Outputs |

| 74F533PMQB | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Transparent Latch with TRI-STATE Outputs |

| 74F533PMX | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Octal Transparent Latch with TRI-STATE Outputs |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。