- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360433 > 74F280 (Fairchild Semiconductor Corporation) 9-Bit Parity Generator/Checker PDF資料下載

參數(shù)資料

| 型號(hào): | 74F280 |

| 廠商: | Fairchild Semiconductor Corporation |

| 英文描述: | 9-Bit Parity Generator/Checker |

| 中文描述: | 9位奇偶發(fā)生器/檢查 |

| 文件頁數(shù): | 2/8頁 |

| 文件大小: | 106K |

| 代理商: | 74F280 |

Philips Semiconductors

Product specification

74F280B

9-bit odd/even parity generator/checker

2

1996 Mar 12

853-0363 16555

FEATURES

High-impedance NPN base inputs for reduced loading

(20

μ

A in Low and High states)

Buffered inputs — one normalized load

Word length easily expanded by cascading

Industrial temperature range available (–40

°

C to +85

°

C)

DESCRIPTION

The 74F280B is a 9-bit Parity Generator or Checker commonly used

to detect errors in high speed data transmission or data retrieval

systems. Both Even (

∑

E

) and Odd (

∑

O

) parity outputs are available

for generating or checking even or odd parity on up to 9 bits.

The Even (

∑

E

) parity output is High when an even number of Data

inputs (I

0

- I

8

) are High. The Odd (

∑

O

) parity output is High when an

odd number of Data inputs are High.

Expansion to larger word sizes is accomplished by tying the Even

(

∑

E

) outputs of up to nine parallel devices to the data inputs of the

final stage. This expansion scheme allows an 81-bit data word to be

checked in less than 20ns.

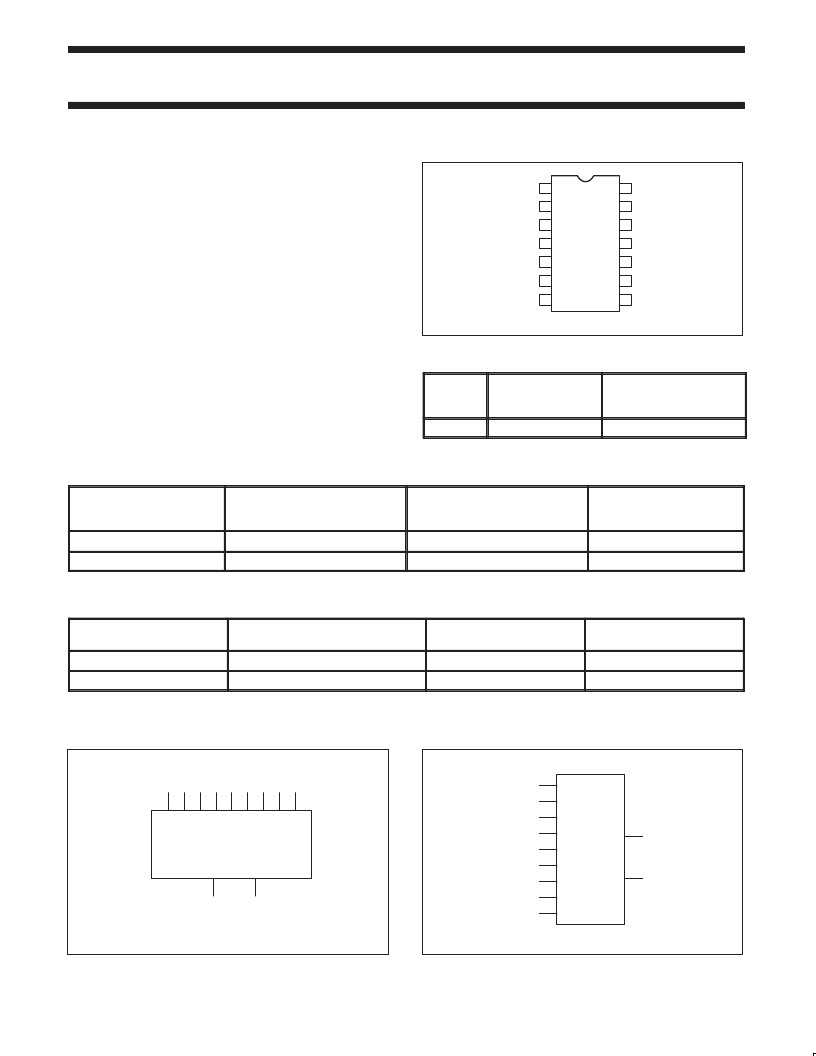

PIN CONFIGURATION

14

13

12

11

10

9

8

7

6

5

4

3

2

1

V

CC

I

5

I

4

I

3

I

2

I

1

I

0

I

6

I

7

I

8

Σ

E

GND

NC

Σ

O

SF00849

TYPE

TYPICAL

PROPAGATION

DELAY

TYPICAL

SUPPLY CURRENT

(TOTAL)

74F280B

5.5ns

26mA

ORDERING INFORMATION

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V

±

10%,

T

amb

= 0

°

C to +70

°

C

INDUSTRIAL RANGE

V

CC

= 5V

±

10%,

T

amb

°

C to +85

°

C

PKG. DWG. #

14-pin plastic DIP

N74F280BN

I74F280BN

SOT27-1

14-pin plastic SO

N74F280BD

I74F280BD

SOT108-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS

DESCRIPTION

74F(U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

I

0

- I

8

Data inputs

1.0/0.033

20

μ

A/20

μ

A

∑

E

,

∑

O

Parity outputs

50/33

1.0mA/20mA

NOTE:

One (1.0) FAST Unit Load is defined as: 20

μ

A in the High state and 0.6mA in the Low state.

LOGIC SYMBOL

8

9

10 11

12 13

1

2

4

5

6

Σ

O

Σ

E

I

0

I

1

I

2

I

3

I

4

I

5

I

6

I

7

I

8

SF00845

IEC/IEEE SYMBOL

8

9

10

11

12

13

1

2

4

5

6

Σ

O

Σ

E

V

=Pin 14

GND=Pin 7

2K

SF00846

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F280PC | 9-Bit Parity Generator/Checker |

| 74F280SC | 9-Bit Parity Generator/Checker |

| 74F280SJ | 9-Bit Parity Generator/Checker |

| 74F283 | 4-bit binary full adder with fast carry(帶快速進(jìn)位的4位二進(jìn)制全加器) |

| 74F2952 | Registered transceiver, non-inverting 3-State |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F280_00 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:9-Bit Parity Generator/Checker |

| 74F280AD | 制造商:NXP Semiconductors 功能描述: |

| 74F280AD TI9215 | 制造商:TI 功能描述:74F280AD |

| 74F280ADSIG91/2 | 制造商:SIG 功能描述:74F280 S1I2B |

| 74F280ADSIG912 | 制造商:SIG 功能描述:74F280 S1I2B |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。