- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360424 > 74F138SJX 3-To-8-Line Demultiplexer PDF資料下載

參數(shù)資料

| 型號(hào): | 74F138SJX |

| 英文描述: | 3-To-8-Line Demultiplexer |

| 中文描述: | 3至8線復(fù)用器 |

| 文件頁(yè)數(shù): | 1/5頁(yè) |

| 文件大小: | 65K |

| 代理商: | 74F138SJX |

2000 Fairchild Semiconductor Corporation

DS009477

www.fairchildsemi.com

April 1988

Revised September 2000

7

74F132

Quad 2-Input NAND Schmitt Trigger

General Description

The F132 contains four 2-input NAND gates which accept

standard TTL input signals and provide standard TTL out-

put levels. They are capable of transforming slowly chang-

ing input signals into sharply defined, jitter-free output

signals. In addition, they have a greater noise margin than

conventional NAND gates.

Each circuit contains a 2-input Schmitt Trigger followed by

level shifting circuitry and a standard FAST

output struc-

ture. The Schmitt Trigger uses positive feedback to effec-

tively speed-up slow input transitions, and provide different

input threshold voltages for positive and negative-going

transitions. This hysteresis between the positive-going and

negative-going input threshold (typically 800 mV) is deter-

mined by resistor ratios and is essentially insensitive to

temperature and supply voltage variations.

Ordering Code:

Devices also available in Tape and Reel. Specify by appending the suffix letter “X” to the ordering code.

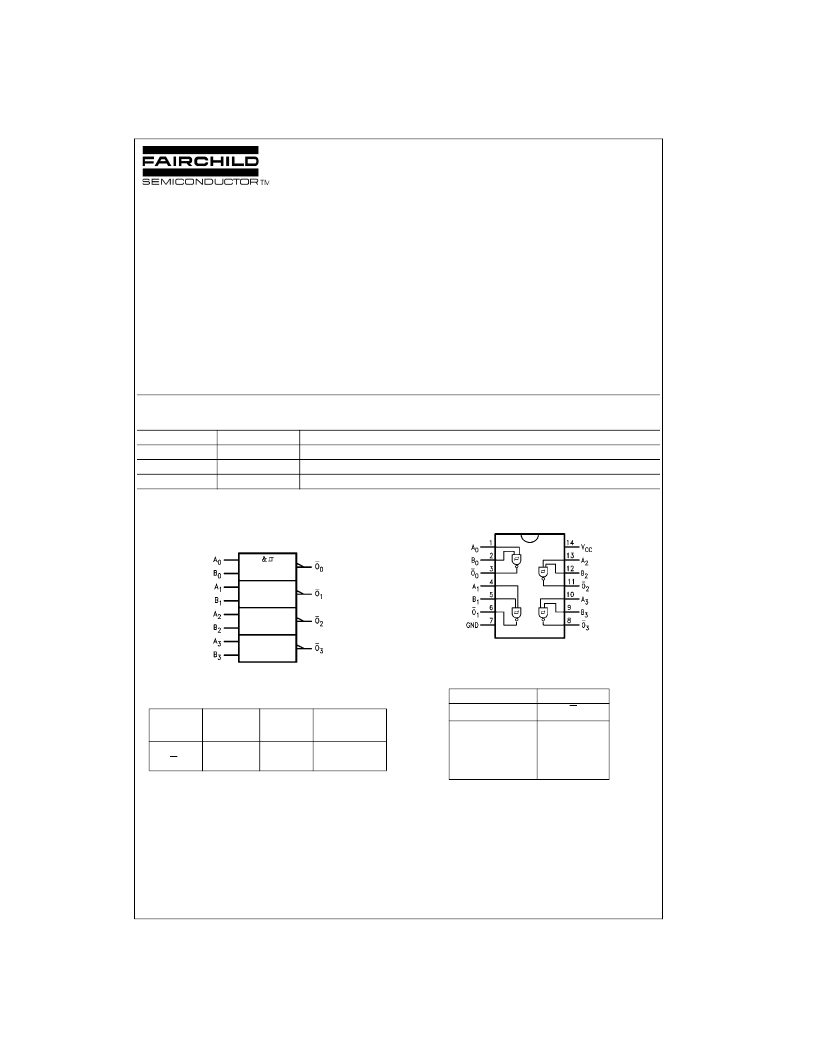

Logic Symbol

IEEE/IEC

Unit Loading/Fan Out

Connection Diagram

Function Table

H

=

HIGH Voltage Level

L

=

LOW Voltage Level

FAST

is a registered trademark of Fairchild Semiconductor Corporation

Order Number

74F132SC

74F132SJ

74F132PC

Package Number

M14A

M14D

N14A

Package Description

14-Lead Small Outline Integrated Circuit (SOIC), JEDEC MS-120, 0.150 Narrow

14-Lead Small Outline Package (SOP), EIAJ TYPE II, 5.3mm Wide

14-Lead Plastic Dual-In-Line Package (PDIP), JEDEC MS-001, 0.300 Wide

Pin Names Description

U.L.

Input I

IH

/I

IL

Output I

OH

/I

OL

20

μ

A/

0.6 mA

1 mA/20 mA

HIGH/LOW

A

n

, B

n

O

n

Inputs

Outputs

1.0/1.0

50/33.3

Inputs

Outputs

A

L

L

H

H

B

L

H

L

H

O

H

H

H

L

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74F132 | Quad 2-input NAND Schmitt trigger(四2輸入與非門施密特觸發(fā)器) |

| 74F133 | 13-input NAND gate(13輸入與非門) |

| 74F138 | 1-of-8 decoder/demultiplexer |

| 74F138SC | .018UFD/250VDC METAL POLY CAP |

| 74F138SJ | 1-of-8 Decoder/Demultiplexer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74F138X6B_BGH UP WAF | 制造商:Rochester Electronics LLC 功能描述: |

| 74F139 | 制造商:NSC 制造商全稱:National Semiconductor 功能描述:Dual 1-of-4 Decoder/Demultiplexer |

| 74F139_00 | 制造商:FAIRCHILD 制造商全稱:Fairchild Semiconductor 功能描述:Dual 1-of-4 Decoder/Demultiplexer |

| 74F139DC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| 74F139LC | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。