- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360412 > 74ALS574AD (NXP SEMICONDUCTORS) Latch flip-flop PDF資料下載

參數(shù)資料

| 型號: | 74ALS574AD |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Latch flip-flop |

| 中文描述: | ALS SERIES, 8-BIT DRIVER, TRUE OUTPUT, PDSO20 |

| 封裝: | PLASTIC, SOT-163, SO-20 |

| 文件頁數(shù): | 2/13頁 |

| 文件大小: | 143K |

| 代理商: | 74ALS574AD |

Philips Semiconductors

Product specification

74ALS573B/74ALS574A

Latch/flip-flop

74ALS573B

74ALS574A

Octal transparent latch (3-State)

Octal D flip-flop (3-State)

2

1991 Feb 08

853–1307 01670

FEATURES

74ALS573B is broadside pinout version of 74ALS373

74ALS574A is broadside pinout version of 74ALS374

Inputs and outputs on opposite side of package allow easy

interface to microprocessors

Useful as an input or output port for microprocessors

3-State outputs for bus interfacing

Common output enable

74ALS563A and 74ALS564A are inverting version of 74ALS573B

and 74ALS574A respectively

DESCRIPTION

The 74ALS573B is an octal transparent latch coupled to eight

3-State output devices. The two sections of the device are controlled

independently by enable (E) and output enable (OE) control gates.

The 74ALS573B is functionally identical to the 74ALS373 but has a

broadside pinout configuration to facilitate PC board layout and

allow easy interface with microprocessors.

The data on the D inputs is transferred to the latch outputs when the

enable (E) input is High. The latch remains transparent to the data

input while E is High, and stores the data that is present one setup

time before the High-to-Low enable transition.

The 74ALS574A is functionally identical to the 74ALS374 but has a

broadside pinout configuration to facilitate PC board layout and

allow easy interface with microprocessors.

It is an 8-bit edge triggered register coupled to eight 3-State output

buffers. The two sections of the device are controlled independently

by clock (CP) and output enable (OE) control gates.

The register is fully edge triggered. The state of the D input, one

setup time before the Low-to-High clock transition is transferred to

the corresponding flip-flop’s Q output.

The active-Low output enable (OE) controls all eight 3-State buffers

independent of the latch operation. When OE is Low, latched or

transparent data appears at the output.

When OE is High, the outputs are in high impedance “off” state,

which means they will neither drive nor load the bus.

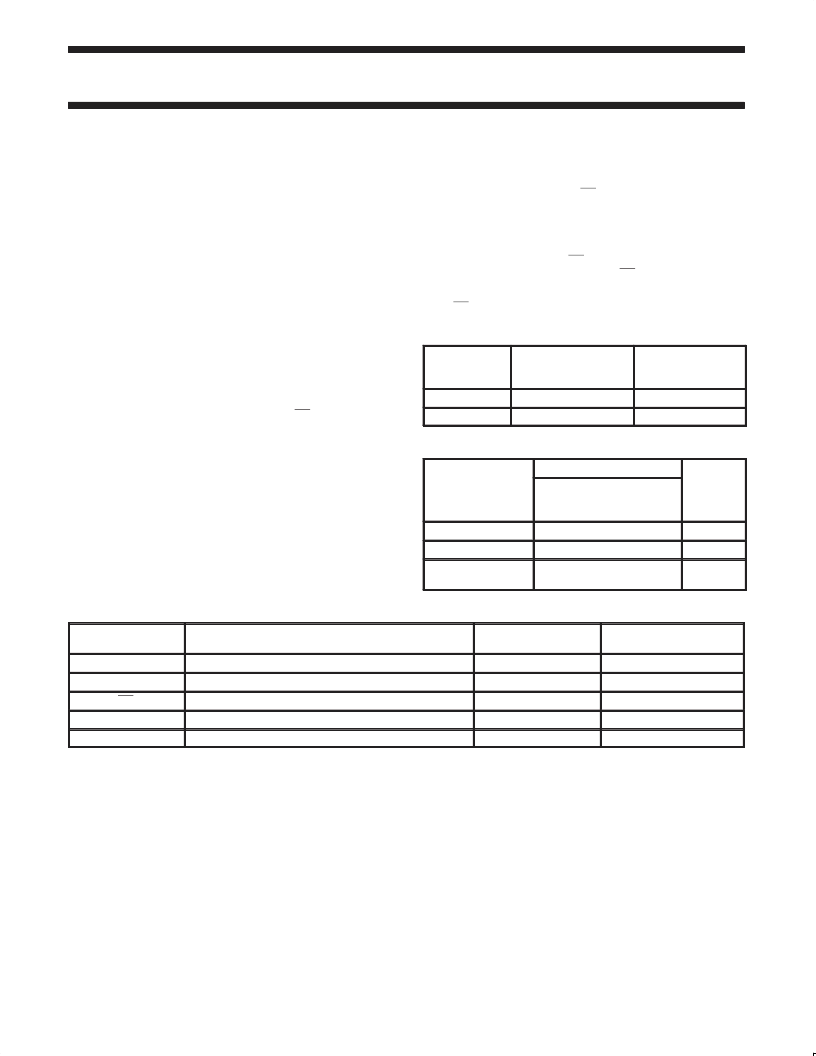

TYPE

TYPICAL

PROPAGATION

DELAY

TYPICAL

SUPPLY CURRENT

(TOTAL)

74ALS573B

5.0ns

12mA

74ALS574A

6.0ns

15mA

ORDERING INFORMATION

ORDER CODE

DESCRIPTION

COMMERCIAL RANGE

V

CC

= 5V

±

10%,

T

amb

= 0

°

C to +70

°

C

DRAWING

NUMBER

20-pin plastic DIP

74ALS573BN, 74ALS574AN

SOT146-1

20-pin plastic SOL

74ALS573BD, 74ALS574AD

SOT163-1

20-pin plastic SSOP

Type II

74ALS573BDB,

74ALS574ADB

SOT339-1

INPUT AND OUTPUT LOADING AND FAN-OUT TABLE

PINS

DESCRIPTION

74ALS (U.L.)

HIGH/LOW

LOAD VALUE

HIGH/LOW

D0 – D7

Data inputs

1.0/1.0

20

μ

A/0.2mA

20

μ

A/0.1mA

20

μ

A/0.1mA

20

μ

A/0.2mA

E (74ALS573B)

Latch enable input

1.0/1.0

OE

Output Enable input (active-Low)

1.0/1.0

CP (74ALS574A)

Clock pulse input (active rising edge)

1.0/2.0

Q0 – Q7

One (1.0) ALS unit load is defined as: 20

μ

A in the High state and 0.1mA in the Low state.

Data outputs

130/240

2.6mA/24mA

NOTE:

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74ALS574ADB | Latch flip-flop |

| 74ALS574AN | Latch flip-flop |

| 74ALS623A-1D | D-Subminiature Connector; No. of Contacts:9; D Sub Shell Size:DB9; Leaded Process Compatible:No; Peak Reflow Compatible (260 C):No RoHS Compliant: No |

| 74ALS623A-1N | D-Subminiature Connector; Gender:Female; No. of Contacts:9; Contact Termination:Solder; D Sub Shell Size:DB9; Body Material:Metal; Contact Plating:Gold Flash |

| 74ALS620A | Transceivers |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74ALS574ADB | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Latch flip-flop |

| 74ALS574AN | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Latch flip-flop |

| 74ALS574NTI88 | 制造商:TI 功能描述:74ALS574N |

| 74ALS620A | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Transceivers |

| 74ALS620A-1 | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Transceivers |

發(fā)布緊急采購,3分鐘左右您將得到回復。