- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360357 > 74ABT5074PW (NXP SEMICONDUCTORS) Synchronizing dual D-type flip-flop with metastable immune characteristics PDF資料下載

參數(shù)資料

| 型號: | 74ABT5074PW |

| 廠商: | NXP SEMICONDUCTORS |

| 元件分類: | 通用總線功能 |

| 英文描述: | Synchronizing dual D-type flip-flop with metastable immune characteristics |

| 中文描述: | ABT SERIES, DUAL POSITIVE EDGE TRIGGERED D FLIP-FLOP, COMPLEMENTARY OUTPUT, PDSO14 |

| 封裝: | 4.40 MM, PLASTIC, MO-153, SOT-402-1, TSSOP1-14 |

| 文件頁數(shù): | 3/7頁 |

| 文件大?。?/td> | 100K |

| 代理商: | 74ABT5074PW |

Philips Semiconductors Advanced BiCMOS Products

Product specification

74ABT5074

Synchronizing dual D-type flip-flop

with metastable immune characteristics

December 15, 1994

3

METASTABLE IMMUNE CHARACTERISTICS

Philips Semiconductors uses the term ‘metastable immune’ to

describe characteristics of some of the products in its family. By

running two independent signal generators (see Figure 1) at nearly

the same frequency (in this case 10MHz clock and 10.02MHz data)

the device-under-test can often be driven into a metastable state. If

the Q output is then used to trigger a digital scope set to infinite

persistence the Q output will build a waveform. An experiment was

run by continuously operating the devices in the region where

metastability will occur.

D

Q

Q

CP

TRIGGER

DIGITAL

SCOPE

INPUT

SIGNAL

GENERATOR

SA00004

SIGNAL

GENERATOR

Figure 1.

Test Setup

After determining the T

0

and

τ

of the flop, calculating the mean time

between failures (MTBF) is simple. Suppose a designer wants to

use the 74ABT5074 for synchronizing asynchronous data that is

arriving at 10MHz (as measured by a frequency counter), has a

clock frequency of 50MHz, and has decided that he would like to

sample the output of the 74ABT5074 7 nanoseconds after the clock

edge. He simply plugs his number into the following equation:

MTBF = e

(t’/

τ

)

/ T

O

*f

C

*f

I

In this formula, f

C

is the frequency of the clock, f

I

is the average

input event frequency, and t’ is the time after the clock pulse that the

output is sampled (t’ > h, h being the normal propagation delay). In

this situation the f

I

will be twice the data frequency of 20 MHz

because input events consist of both of low and high transitions.

Multiplying f

I

by f

C

gives an answer of 10

15

Hz

2

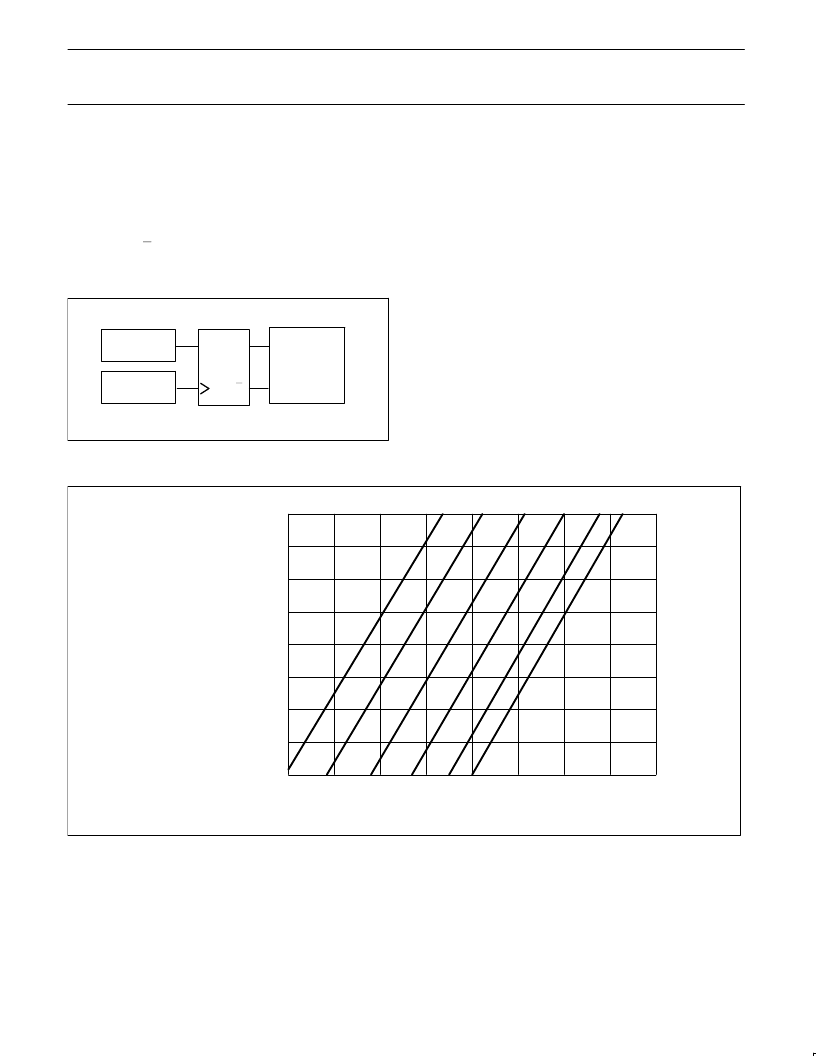

. From Figure 2 it is

clear that the MTBF is greater than 10

10

seconds. Using the above

formula the actual MTBF is 1.69

×

10

10

seconds or about 535 years.

E6

E8

E10

E12

E14

E15 = fc*fi

E13

E12

E11

E10

E9

E8

E7

E6

E5

10,000 YEARS

100 YEARS

ONE YEAR

ONE WEEK

MTBF

(SECONDS)

t’ (NANOSECONDS)

4

5

6

7

8

MTBF = e

(t’/

τ

)

/T

O

*f

C

*f

I

SA00005

V

CC

= 5V, T

amb

= 25

°

C,

τ

=94ps, To = 1.3x10

7

sec

Figure 2.

Mean Time Between Failures (MTBF) versus t’

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 74ABT5074DB | Synchronizing dual D-type flip-flop with metastable immune characteristics |

| 74ABT534APWDH | Octal D-type flip-flop, inverting 3-State |

| 74ABT534A | Octal D-type flip-flop, inverting(3-State)(八反相(三態(tài))D觸發(fā)器) |

| 74ABT534AD | Octal D-type flip-flop, inverting 3-State |

| 74ABT534ADB | Octal D-type flip-flop, inverting 3-State |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 74ABT5074PW-T | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Dual D-Type Flip-Flop |

| 74ABT534A | 制造商:IRF 制造商全稱:International Rectifier 功能描述:Octal D-type flip-flop, inverting (3-State) |

| 74ABT534AD | 制造商:PHILIPS 制造商全稱:NXP Semiconductors 功能描述:Octal D-type flip-flop, inverting 3-State |

| 74ABT534AD,112 | 功能描述:觸發(fā)器 OCTAL D F/F INV 3-S RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

| 74ABT534AD,118 | 功能描述:觸發(fā)器 OCTAL D F/F INV 3-S RoHS:否 制造商:Texas Instruments 電路數(shù)量:2 邏輯系列:SN74 邏輯類型:D-Type Flip-Flop 極性:Inverting, Non-Inverting 輸入類型:CMOS 輸出類型: 傳播延遲時間:4.4 ns 高電平輸出電流:- 16 mA 低電平輸出電流:16 mA 電源電壓-最大:5.5 V 最大工作溫度:+ 85 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:X2SON-8 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。