- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄360280 > 5962R9858302QXXC (Aeroflex Inc.) PowerCap PDF資料下載

參數(shù)資料

| 型號(hào): | 5962R9858302QXXC |

| 廠商: | Aeroflex Inc. |

| 英文描述: | PowerCap |

| 中文描述: | 20MHz的16位微控制器 |

| 文件頁數(shù): | 20/43頁 |

| 文件大小: | 186K |

| 代理商: | 5962R9858302QXXC |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁

20

41

TUO

BHE

Low

Byte High Enable. The assertion of the BHE signal will occur

for all 16-bit word writes, and high byte writes in both 8- and 16-

bit wide bus cycles.

Setting CCR.2 = 1 enables the BHE function of pin 41.

TUO

WRH

Low

Write High. The WRH signal is asserted for high byte writes,

and word writes for 16-bit wide bus cycles. Additionally, WRH

is asserted for all write operations when using an 8-bit wide bus

cycle.

Setting CCR.2 = 0 enables the WRH function of pin 41.

42

TI

P2.4

---

Port 2 Pin 4. An input only port pin that is read at location 10h

of HWindow 0.

TI

T2RST

High

Timer 2 Reset. Asserting the T2RST signal will reset Timer 2.

To enable the T2RST function of pin 42, set IOC0.3 = 1 and

IOC0.5 = 0.

43

TI

READY

High

READY input. The READY signal is used to lengthen memory

cycles by inserting “wait states” for interfacing to slow peripher-

als. When the READY signal is high, no “wait states” are gener-

ated, and the CPU operation continues in a normal fashion. If

READY is low during the falling edge of CLKOUT, the mem-

ory controller inserts “wait states” into the memory cycle. “Wait

state” generation will continue until a falling edge of CLKOUT

detects READY as logically high, or until the number of “wait

states” is equal to the number programmed into CCR.4 and

CCR.5.

Note: The READY signal is only used for external memory

accesses, and is functional during the CCR fetch.

44

TI

P2.3

---

Port 2 Pin 3. An input only port pin that is read at location 10h

of HWindow 0.

TI

T2CLK

---

Timer 2 Clock input. Setting IOC0.7 = 0 and IOC3.0 = 0

enables this pin as the external clock source for Timer 2.

IOC0.7:

IOC3.0:

Timer 2 Clock Source:

X 1 Internal Clock Source

0 0 P2.3 External Clock Source

1 0 HSI.1 External Clock Source

45

TUB

AD15

---

Bit 15 of the Address/Data bus. This pin is a dedicated address

pin when operating with 8-bit wide bus cycles. For 16-bit wide

bus cycles, this pin is used as multiplexed address and data.

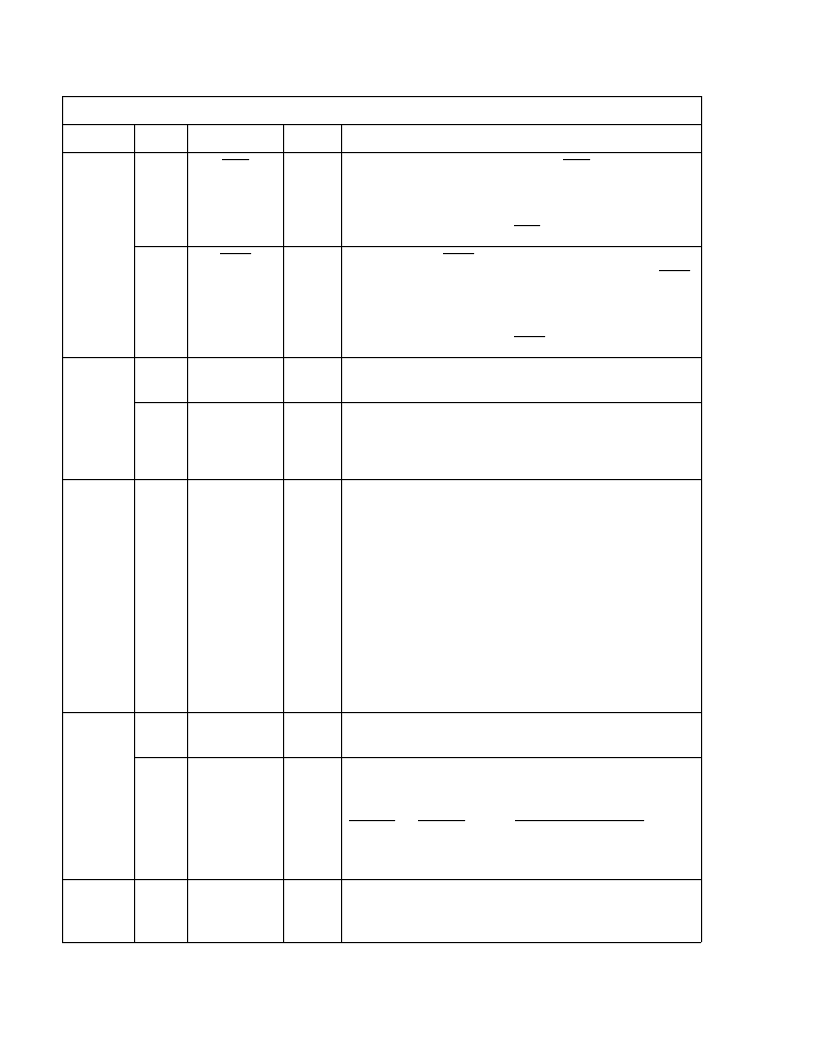

Table 10: 68-lead Flat Pack Pin Descriptions

QFP Pin#

I/O

Name

Active

Description

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 5962R9858302VXA | PowerCap with Crystal |

| 5962R9858302VXC | 20MHz 16-bit Microcontroller |

| 5962R9858302VXX | iButton Probe |

| 5962R9858302VXXA | iButton Probe |

| 5962R9858302VXXC | iButton Probe |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 5962R9863601VGA | 制造商:Analog Devices 功能描述: |

| 5962R9863602VGA | 制造商:Analog Devices 功能描述:OP AMP, JFET-INPUT - Rail/Tube |

| 5962R9863701VGA | 制造商:Analog Devices 功能描述:- Rail/Tube |

| 5962R9863701VHA | 制造商:Analog Devices 功能描述:AEROSPACE LOW INPUT CURRENT OPERATIONAL AMPLIFIER - Rail/Tube |

| 5962R9863701VPA | 制造商:Analog Devices 功能描述:OP AMP, GENERAL PURPOSE - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。