- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄34467 > 550PCFREQBGR (SILICON LABORATORIES) VCXO, CLOCK, 10 MHz - 160 MHz, CMOS OUTPUT PDF資料下載

參數(shù)資料

| 型號: | 550PCFREQBGR |

| 廠商: | SILICON LABORATORIES |

| 元件分類: | VCXO, clock |

| 英文描述: | VCXO, CLOCK, 10 MHz - 160 MHz, CMOS OUTPUT |

| 封裝: | ROHS COMPLIANT PACKAGE-6 |

| 文件頁數(shù): | 34/45頁 |

| 文件大?。?/td> | 691K |

| 代理商: | 550PCFREQBGR |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁當(dāng)前第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁

Si550

4

Rev. 0.5

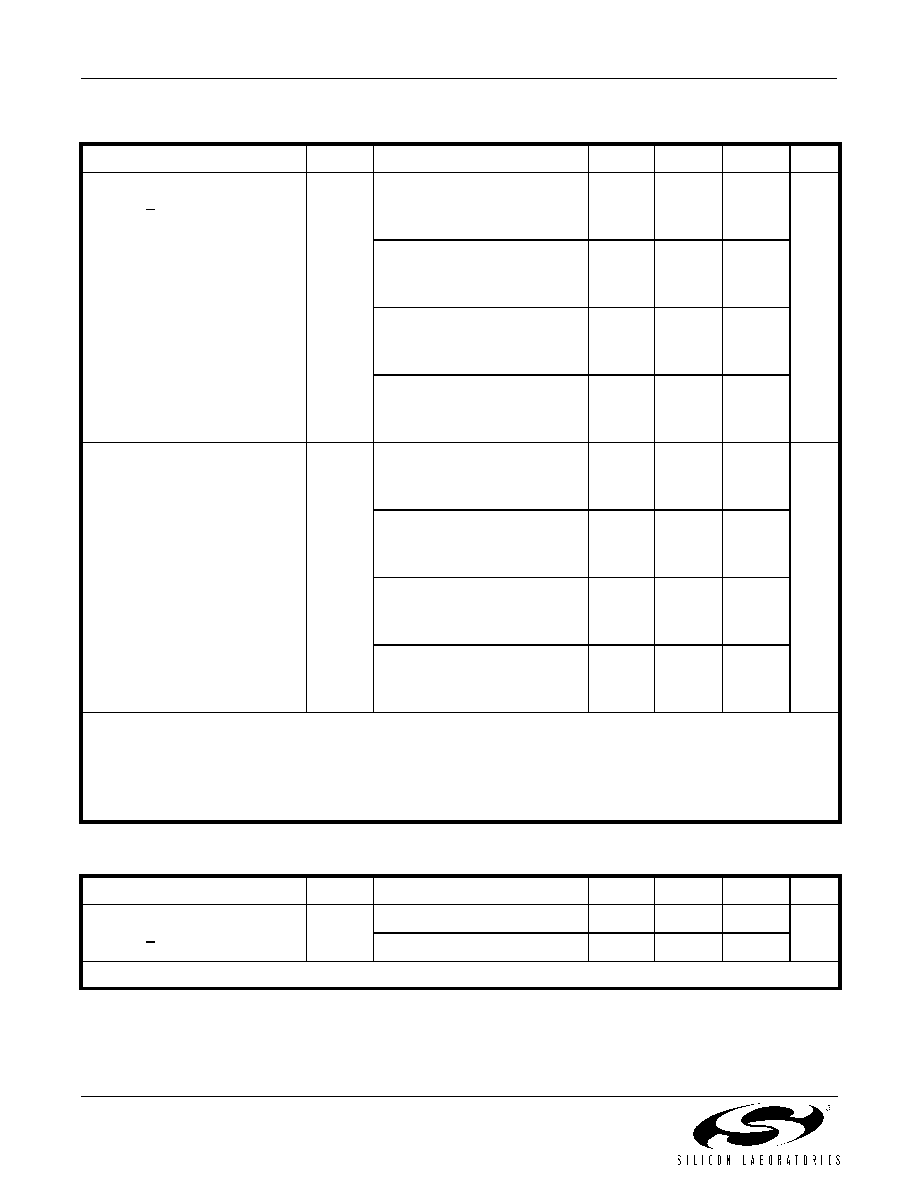

Table 5. CLK± Output Phase Jitter

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Phase Jitter (RMS)1,2,3

for FOUT > 500 MHz

φ

J

Kv = 45 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.35

0.38

—

ps

Kv = 90 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.43

0.41

—

Kv = 135 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.52

0.46

—

Kv = 180 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.64

0.52

—

Phase Jitter (RMS)1,2,3

for FOUT of 125 to 500 MHz

φ

J

Kv = 45 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.42

0.58

—

ps

Kv = 90 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.48

0.60

—

Kv = 135 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.57

0.64

—

Kv = 180 ppm/V

12 kHz to 20 MHz (OC-48)

50 kHz to 80 MHz (OC-192)

—

0.67

0.68

—

Notes:

1. Differential Modes: LVPECL/LVDS/CML. Refer to AN255, AN256, and AN266 for further information.

2. For best jitter and phase noise performance, always choose the smallest KV that meets the application’s minimum APR

requirements. See “AN266: VCXO Tuning Slope (KV), Stability, and Absolute Pull Range (APR)” for more information.

3. See “AN255: Replacing 622 MHz VCSO devices with the Si550 VCXO” for comparison highlighting power supply

rejection (PSR) advantage of Si55x versus SAW-based solutions.

Table 6. CLK± Output Period Jitter

Parameter

Symbol

Test Condition

Min

Typ

Max

Units

Period Jitter*

for FOUT < 160 MHz

JPER

RMS

—

2

—

ps

Peak-to-Peak

—

14

—

*Note: Any output mode, including CMOS, LVPECL, LVDS, CML. N = 1000 cycles. Refer to AN279 for further information.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| 550UCFREQBG | VCXO, CLOCK, 10 MHz - 945 MHz, CMOS OUTPUT |

| 550WFFREQBG | VCXO, CLOCK, 10 MHz - 945 MHz, CMOS OUTPUT |

| 550BDFREQBGR | VCXO, CLOCK, 10 MHz - 945 MHz, LVDS OUTPUT |

| 550ACFREQBGR | VCXO, CLOCK, 10 MHz - 945 MHz, LVPECL OUTPUT |

| 550WA155M520BGR | VCXO, CLOCK, 155.52 MHz, LVCMOS OUTPUT |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| 550PD10M2400DG | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Trays |

| 550PD10M2400DGR | 制造商:Silicon Laboratories Inc 功能描述:OSCILLATOR - Tape and Reel |

| 550PE19M4400DG | 制造商:Silicon Laboratories Inc 功能描述:CNTRLD OSC 19.44MHZ VCXO CMOS 6SMD - Trays |

| 550PG50M4000DG | 功能描述:VCXO振蕩器 SINGLE VCXO 6 PIN 0.5PS RS JTR RoHS:否 制造商:Fox 封裝 / 箱體:5 mm x 3.2 mm 頻率:19.2 Mhz 頻率穩(wěn)定性:2.5 PPM 輸出格式: 封裝:Reel 電源電壓:3 V 端接類型:SMD/SMT 尺寸:3.2 mm W x 5 mm L x 1.5 mm H 最小工作溫度:- 20 C 最大工作溫度:+ 75 C |

| 550PG74M2500DG | 功能描述:VCXO振蕩器 SNGL VCXO 6 PIN 7mm x 5mm RoHS:否 制造商:Fox 封裝 / 箱體:5 mm x 3.2 mm 頻率:19.2 Mhz 頻率穩(wěn)定性:2.5 PPM 輸出格式: 封裝:Reel 電源電壓:3 V 端接類型:SMD/SMT 尺寸:3.2 mm W x 5 mm L x 1.5 mm H 最小工作溫度:- 20 C 最大工作溫度:+ 75 C |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。