- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375033 > XCV812E-6FG676C (Xilinx, Inc.) Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號: | XCV812E-6FG676C |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| 中文描述: | 的Virtex娥內(nèi)存擴展1.8伏現(xiàn)場可編程門陣列 |

| 文件頁數(shù): | 7/116頁 |

| 文件大小: | 1087K |

| 代理商: | XCV812E-6FG676C |

第1頁第2頁第3頁第4頁第5頁第6頁當前第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

DS025-2 (v2.1) July 17, 2002

www.xilinx.com

1-800-255-7778

Module 2 of 4

3

R

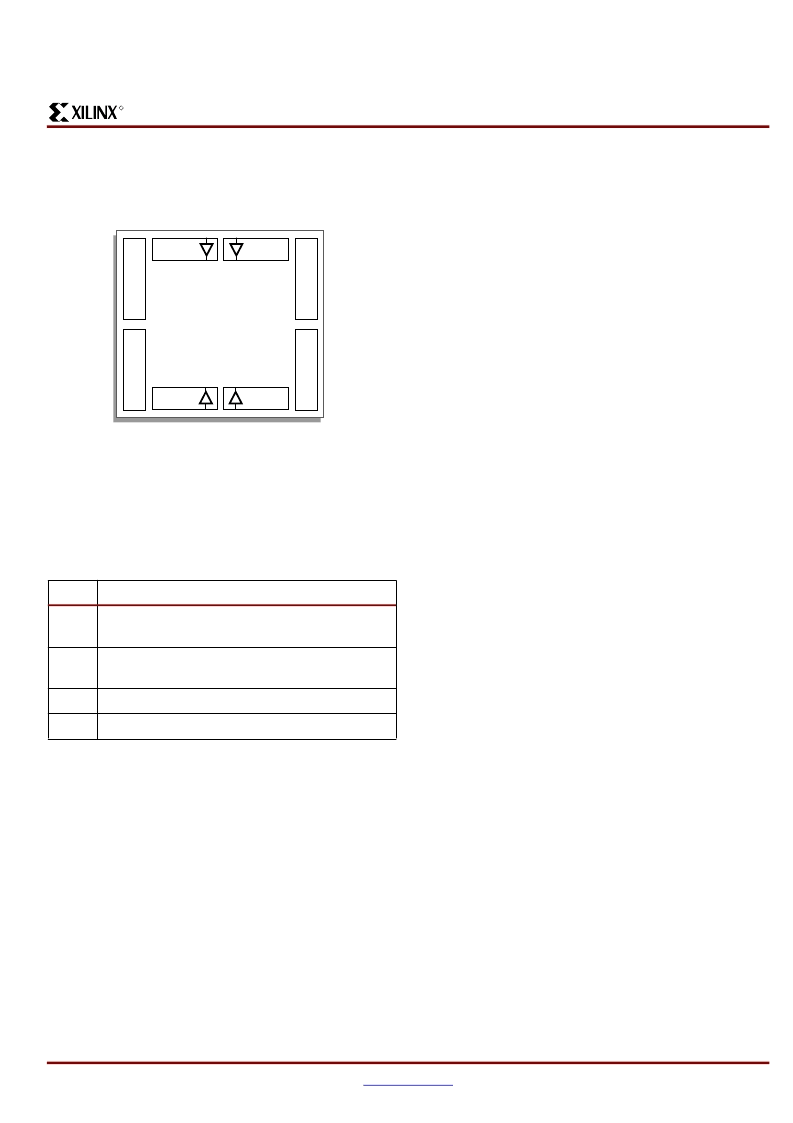

Eight I/O banks result from separating each edge of the

FPGA into two banks, as shown in

Figure 3

. Each bank has

multiple V

CCO

pins, all of which must be connected to the

same voltage. This voltage is determined by the output

standards in use.

Within a bank, output standards can be mixed only if they

use the same V

CCO

. Compatible standards are shown in

Table 2

. GTL and GTL+ appear under all voltages because

their open-drain outputs do not depend on V

CCO

.

Some input standards require a user-supplied threshold

voltage, V

REF

. In this case, certain user-I/O pins are auto-

matically configured as inputs for the V

REF

voltage. Approx-

imately one in six of the I/O pins in the bank assume this

role.

The V

REF

pins within a bank are interconnected internally

and consequently only one V

REF

voltage can be used within

each bank. All V

REF

pins in the bank, however, must be con-

nected to the external voltage source for correct operation.

Within a bank, inputs that require V

REF

can be mixed with

those that do not. However, only one V

REF

voltage can be

used within a bank.

In Virtex-E, input buffers with LVTTL, LVCMOS2,

LVCMOS18, PCI33_3, PCI66_3 standards are supplied by

V

CCO

rather than V

CCINT

. For these standards, only input

and output buffers that have the same V

CCO

can be mixed

together.

The V

CCO

and V

REF

pins for each bank appear in the device

pin-out tables and diagrams. The diagrams also show the

bank affiliation of each I/O.

Within a given package, the number of V

REF

and V

CCO

pins

can vary depending on the size of device. In larger devices,

more I/O pins convert to V

REF

pins. Since these are always

a super set of the V

REF

pins used for smaller devices, it is

possible to design a PCB that permits migration to a larger

device if necessary. All the V

REF

pins for the largest device

anticipated must be connected to the V

REF

voltage, and not

used for I/O.

In smaller devices, some V

CCO

pins used in larger devices

do not connect within the package. These unconnected pins

can be left unconnected externally, or they can be con-

nected to the V

CCO

voltage to permit migration to a larger

device, if necessary.

Configurable Logic Block

The basic building block of the Virtex-E CLB is the logic cell

(LC). An LC includes a 4-input function generator, carry

logic, and a storage element. The output from the function

generator in each LC drives both the CLB output and the D

input of the flip-flop. Each Virtex-E CLB contains four LCs,

organized in two similar slices, as shown in

Figure 4

.

Figure 5

shows a more detailed view of a single slice.

Figure 3:

Virtex-E I/O Banks

Table 2:

Compatible Output Standards

V

CCO

Compatible Standards

3.3 V

PCI, LVTTL, SSTL3 I, SSTL3 II, CTT, AGP, GTL,

GTL+, LVPECL

2.5 V

SSTL2 I, SSTL2 II, LVCMOS2, GTL, GTL+,

BLVDS, LVDS

1.8 V

LVCMOS18, GTL, GTL+

1.5 V

HSTL I, HSTL III, HSTL IV, GTL, GTL+

ds022_03_121799

Bank 0

GCLK3 GCLK2

GCLK1 GCLK0

Bank 1

Bank 5

Bank 4

VirtexE

Device

B

B

B

B

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCV812E-6FG676I | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG900C | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG900I | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404C | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404I | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV812E-6FG676I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG900C | 功能描述:IC FPGA 1.8V C-TEMP 900-FBGA RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:Virtex®-E EM 產(chǎn)品變化通告:XC4000(E,L) Discontinuation 01/April/2002 標準包裝:24 系列:XC4000E/X LAB/CLB數(shù):100 邏輯元件/單元數(shù):238 RAM 位總計:3200 輸入/輸出數(shù):80 門數(shù):3000 電源電壓:4.5 V ~ 5.5 V 安裝類型:表面貼裝 工作溫度:-40°C ~ 100°C 封裝/外殼:120-BCBGA 供應商設(shè)備封裝:120-CPGA(34.55x34.55) |

| XCV812E-6FG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-7BG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復。