- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄375033 > XCV812E-6BG676I (Xilinx, Inc.) Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號: | XCV812E-6BG676I |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| 中文描述: | 的Virtex娥內(nèi)存擴(kuò)展1.8伏現(xiàn)場可編程門陣列 |

| 文件頁數(shù): | 16/116頁 |

| 文件大小: | 1087K |

| 代理商: | XCV812E-6BG676I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁當(dāng)前第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁

Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays

Module 2 of 4

12

www.xilinx.com

1-800-255-7778

DS025-2 (v2.1) July 17, 2002

R

tions and the desired performance. Finally, the router inter-

connects the blocks.

The PAR algorithms support fully automatic implementation

of most designs. For demanding applications, however, the

user can exercise various degrees of control over the pro-

cess. User partitioning, placement, and routing information

is optionally specified during the design-entry process. The

implementation of highly structured designs can benefit

greatly from basic floor planning.

The implementation software incorporates Timing Wizard

timing-driven placement and routing. Designers specify tim-

ing requirements along entire paths during design entry.

The timing path analysis routines in PAR then recognize

these user-specified requirements and accommodate them.

Timing requirements are entered on a schematic in a form

directly relating to the system requirements, such as the tar-

geted clock frequency, or the maximum allowable delay

between two registers. In this way, the overall performance

of the system along entire signal paths is automatically tai-

lored to user-generated specifications. Specific timing infor-

mation for individual nets is unnecessary.

Design Verification

In addition to conventional software simulation, FPGA users

can use in-circuit debugging techniques. Because Xilinx

devices are infinitely reprogrammable, designs can be veri-

fied in real time without the need for extensive sets of soft-

ware simulation vectors.

The development system supports both software simulation

and in-circuit debugging techniques. For simulation, the

system extracts the post-layout timing information from the

design database, and back-annotates this information into

the net list for use by the simulator. Alternatively, the user

can verify timing-critical portions of the design using the

TRCE

static timing analyzer.

For in-circuit debugging, an optional download and read-

back cable is available. This cable connects the FPGA in the

target system to a PC or workstation. After downloading the

design into the FPGA, the designer can single-step the

logic, readback the contents of the flip-flops, and so observe

the internal logic state. Simple modifications can be down-

loaded into the system in a matter of minutes.

Configuration

Virtex-E devices are configured by loading configuration

data into the internal configuration memory. Note that

attempting to load an incorrect bitstream causes configura-

tion to fail and can damage the device.

Some of the pins used for configuration are dedicated pins,

while others can be re-used as general purpose inputs and

outputs once configuration is complete.

The following are dedicated pins:

Mode pins (M2, M1, M0)

Configuration clock pin (CCLK)

PROGRAM pin

DONE pin

Boundary-scan pins (TDI, TDO, TMS, TCK)

Depending on the configuration mode chosen, CCLK can

be an output generated by the FPGA, or it can be generated

externally and provided to the FPGA as an input. For correct

operation, these pins require a V

CCO

of 3.3 V to permit

LVTTL operation. All of the pins affected are in banks 2 or 3.

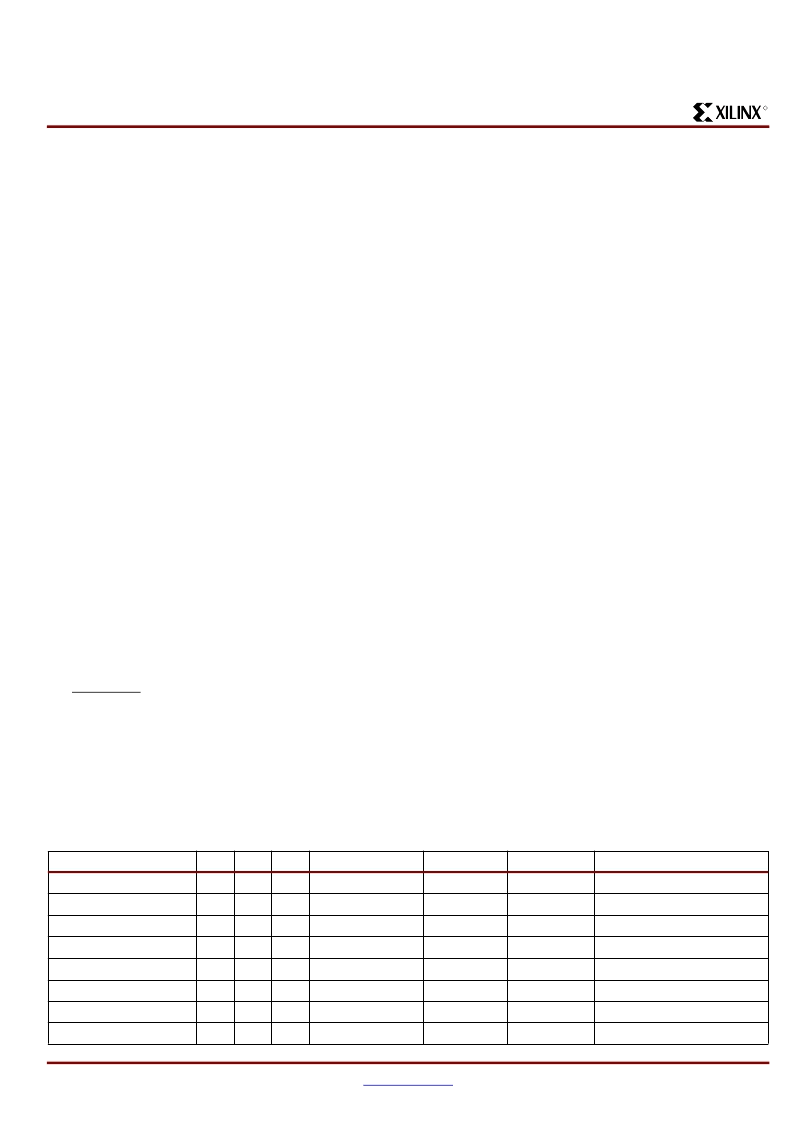

Table 8:

Configuration Codes

Configuration Modes

Virtex-E supports the following four configuration modes.

Slave-serial mode

Master-serial mode

SelectMAP mode

Boundary-scan mode (JTAG)

The Configuration mode pins (M2, M1, M0) select among

these configuration modes with the option in each case of

having the IOB pins either pulled up or left floating prior to

configuration. The selection codes are listed in

Table 8

.

Configuration through the boundary-scan port is always

available, independent of the mode selection. Selecting the

boundary-scan mode simply turns off the other modes. The

three mode pins have internal pull-up resistors, and default

to a logic High if left unconnected.

Configuration Mode

Master-serial mode

Boundary-scan mode

SelectMAP mode

Slave-serial mode

Master-serial mode

Boundary-scan mode

SelectMAP mode

Slave-serial mode

M2

0

1

1

1

1

0

0

0

M1

0

0

1

1

0

0

1

1

M0

0

1

0

1

0

1

0

1

CCLK Direction

Out

N/A

In

In

Out

N/A

In

In

Data Width

1

1

8

1

1

1

8

1

Serial D

out

Yes

No

No

Yes

Yes

No

No

Yes

Configuration Pull-ups

No

No

No

No

Yes

Yes

Yes

Yes

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XCV812E-6BG900C | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6BG900I | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG404C | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG404I | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG556C | Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XCV812E-6BG900C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6BG900I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG404C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG404I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

| XCV812E-6FG556C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-E 1.8 V Extended Memory Field Programmable Gate Arrays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。