- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374257 > K4E661612C-45 (SAMSUNG SEMICONDUCTOR CO. LTD.) 4M x 16bit CMOS Dynamic RAM with Extended Data Out PDF資料下載

參數(shù)資料

| 型號(hào): | K4E661612C-45 |

| 廠商: | SAMSUNG SEMICONDUCTOR CO. LTD. |

| 英文描述: | 4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| 中文描述: | 4米× 16位的CMOS動(dòng)態(tài)隨機(jī)存儲(chǔ)器的擴(kuò)展數(shù)據(jù)輸出 |

| 文件頁數(shù): | 29/36頁 |

| 文件大小: | 884K |

| 代理商: | K4E661612C-45 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當(dāng)前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁

CMOS DRAM

K4E661612C,K4E641612C

t

ASC

RAS

V

IH

-

V

IL

-

A

V

IH

-

V

IL

-

W

V

IH

-

V

IL

-

OE

V

IH

-

V

IL

-

V

I/OH

-

V

I/OL

-

DQ0 ~ DQ7

ROW

ADDR

t

CSH

t

RASP

t

RP

t

ASR

Don

′

t care

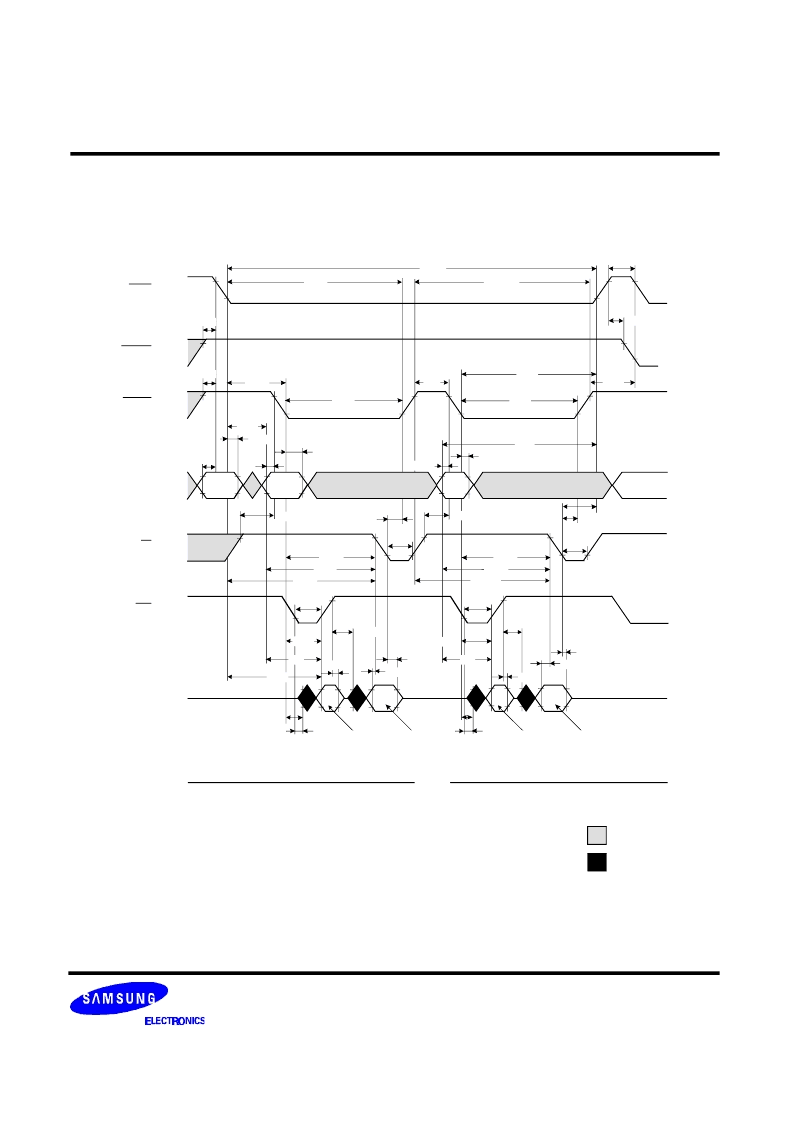

HYPER PAGE MODE LOWER BYTE READ - MODIFY - WRITE CYCLE

Undefined

t

RAD

t

CAH

t

WP

t

DH

COL.

ADDR

COL.

ADDR

t

ASC

t

CAH

t

RAL

t

RCS

t

CWL

t

CWD

t

AWD

t

RWD

t

WP

t

CWD

t

AWD

t

CPWD

t

CWL

t

AA

t

RAC

t

OEA

t

CLZ

t

CAC

t

OEZ

t

OED

t

CLZ

t

OEA

t

CAC

t

AA

t

DH

t

OED

t

RWL

t

RCD

t

CP

t

CAS

t

CAS

t

CRP

t

CRP

t

CRP

V

I/OH

-

V

I/OL

-

DQ8 ~ DQ15

t

DS

t

OEZ

VALID

DATA-OUT

VALID

DATA-IN

VALID

DATA-OUT

VALID

DATA-IN

t

DS

t

RPC

t

RSH

OPEN

LCAS

V

IH

-

V

IL

-

UCAS

V

IH

-

V

IL

-

t

HPRWC

t

RCS

t

OLZ

t

OLZ

t

RAH

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| K4E661612C-50 | 4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E661612C-60 | 4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E641612C-TC | 4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E641612C-TC45 | 4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E641612C-TC50 | 4M x 16bit CMOS Dynamic RAM with Extended Data Out |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| K4E661612C-50 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E661612C-60 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E661612C-L | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E661612C-L45 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 16bit CMOS Dynamic RAM with Extended Data Out |

| K4E661612C-L50 | 制造商:SAMSUNG 制造商全稱:Samsung semiconductor 功能描述:4M x 16bit CMOS Dynamic RAM with Extended Data Out |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。