- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374982 > XC3195A-09PG175C (XILINX INC) Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) PDF資料下載

參數(shù)資料

| 型號: | XC3195A-09PG175C |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| 中文描述: | FPGA, 484 CLBS, 6500 GATES, 370 MHz, CPGA175 |

| 封裝: | CERAMIC, PGA-175 |

| 文件頁數(shù): | 11/50頁 |

| 文件大?。?/td> | 474K |

| 代理商: | XC3195A-09PG175C |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

2-113

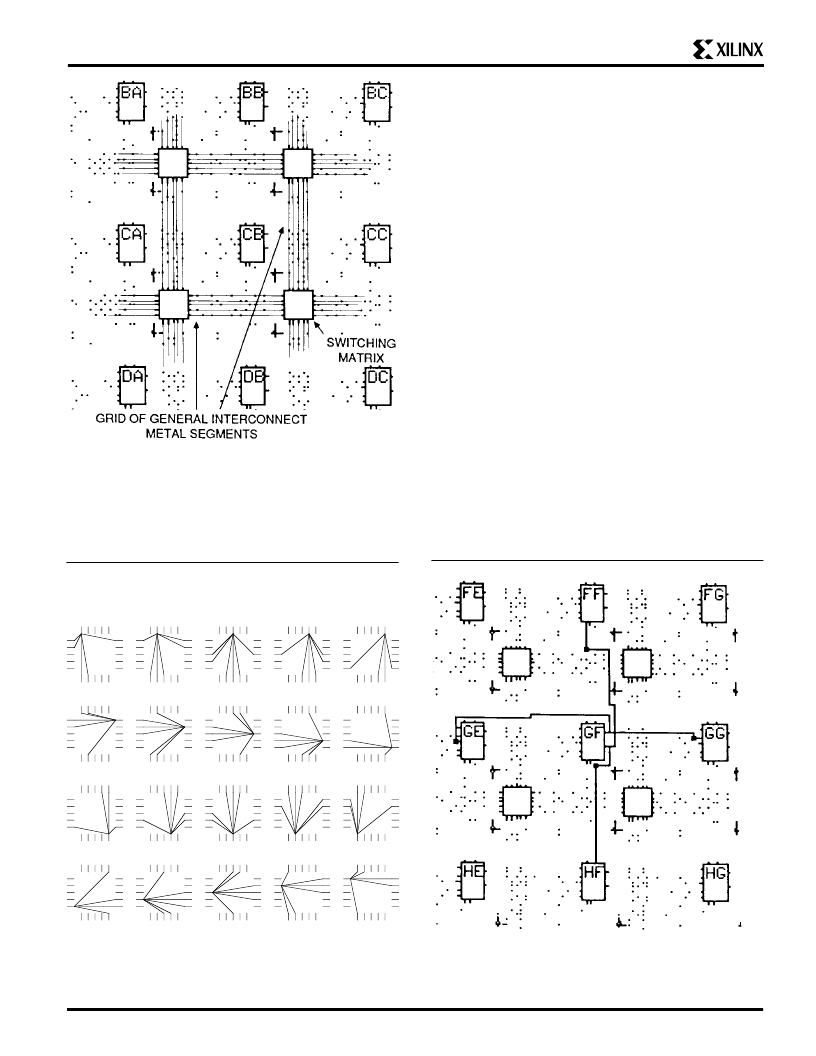

Figure 10.

Switch Matrix Interconnection Options for Each

Pin.

Switch matrices on the edges are different. Use Show

Matrix menu option in the XACT system

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

1105 13

Special buffers within the general interconnect areas pro-

vide periodic signal isolation and restoration for improved

performance of lengthy nets. The interconnect buffers are

available to propagate signals in either direction on a given

general interconnect segment. These bidirectional (bidi)

buffers are found adjacent to the switching matrices,

above and to the right and may be highlighted by the use

of the Show BIDI command in the XACT system. The other

PIPs adjacent to the matrices are accessed to or from

Longlines. The development system automatically de-

fines the buffer direction based on the location of the

interconnection network source. The delay calculator of

the XACT development system automatically calculates

and displays the block, interconnect and buffer delays for

any paths selected. Generation of the simulation netlist

with a worst-case delay model is provided by an XACT

option.

Direct Interconnect

Direct interconnect, shown in Figure 11, provides the most

efficient implementation of networks between adjacent

CLBs or I/O Blocks. Signals routed from block to block

using the direct interconnect exhibit minimum interconnect

propagation and use no general interconnect resources.

For each CLB, the X output may be connected directly to

the B input of the CLB immediately to its right and to the C

input of the CLB to its left. The Y output can use direct

interconnect to drive the D input of the block immediately

above and the A input of the block below. Direct intercon-

X2664

Figure 9.

LCA General-Purpose Interconnect.

Composed of a grid of metal segments that may be intercon-

nected through switch matrices to form networks for CLB and

IOB inputs and outputs.

Figure 11.

CLB X and Y Outputs.

The X and Y outputs of each CLB have single contact, direct

access to inputs of adjacent CLBs

X2663

相關PDF資料 |

PDF描述 |

|---|---|

| XC3195A-09PP175C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3195A-09PQ160C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3195A-09PQ208C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3195A-1PC84C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3195A-1PP175C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

相關代理商/技術參數(shù) |

參數(shù)描述 |

|---|---|

| XC3195A-09PQ160C | 功能描述:IC FPGA 7500 GATE 160-PQFP RoHS:否 類別:集成電路 (IC) >> 嵌入式 - FPGA(現(xiàn)場可編程門陣列) 系列:XC3000A/L 標準包裝:1 系列:Kintex-7 LAB/CLB數(shù):25475 邏輯元件/單元數(shù):326080 RAM 位總計:16404480 輸入/輸出數(shù):350 門數(shù):- 電源電壓:0.97 V ~ 1.03 V 安裝類型:表面貼裝 工作溫度:0°C ~ 85°C 封裝/外殼:900-BBGA,F(xiàn)CBGA 供應商設備封裝:900-FCBGA(31x31) 其它名稱:122-1789 |

| XC3195A-1PC84C | 制造商:Xilinx 功能描述: |

| XC3195A-1PQ160C | 制造商:Xilinx 功能描述: |

| XC3195A-1PQ208C | 制造商:Xilinx 功能描述: |

| XC3195A-2PC84C | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。