- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374983 > XC3042A-7PC84I (XILINX INC) ECONOLINE: RSS & RSD - 1kVDC and 3KVDC Isolation- Internal SMD Construction- UL94V-0 Package Material- Toroidal Magnetics- Efficiency to 85%- SMD5, SMD8, SMD10 and SMD12 case styles PDF資料下載

參數(shù)資料

| 型號: | XC3042A-7PC84I |

| 廠商: | XILINX INC |

| 元件分類: | FPGA |

| 英文描述: | ECONOLINE: RSS & RSD - 1kVDC and 3KVDC Isolation- Internal SMD Construction- UL94V-0 Package Material- Toroidal Magnetics- Efficiency to 85%- SMD5, SMD8, SMD10 and SMD12 case styles |

| 中文描述: | FPGA, 144 CLBS, 2000 GATES, 113 MHz, PQCC84 |

| 封裝: | PLASTIC, LCC-84 |

| 文件頁數(shù): | 29/50頁 |

| 文件大小: | 474K |

| 代理商: | XC3042A-7PC84I |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁當前第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁

2-131

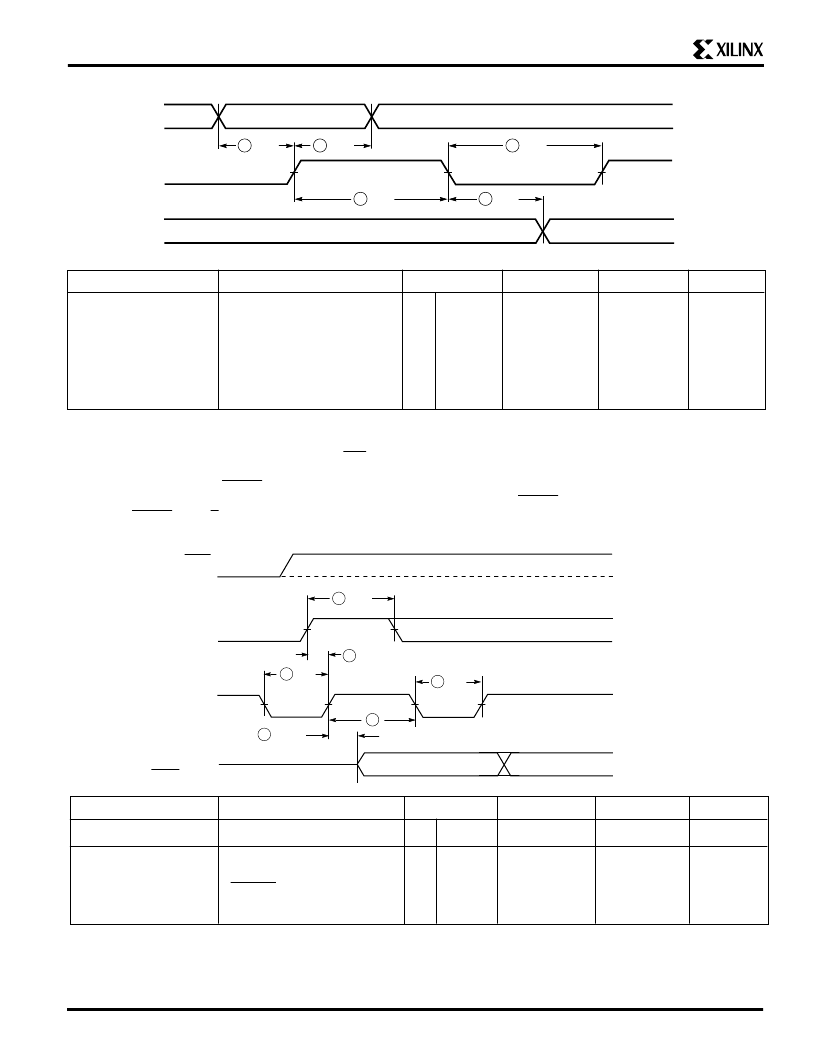

Program Readback Switching Characteristics

Description

Symbol

Min

Max

Units

CCLK

To DOUT

3

T

CCO

100

ns

DIN setup

DIN hold

High time

Low time (Note 1)

Frequency

1

2

4

5

T

DCC

T

CCD

T

CCH

T

CCL

F

CC

60

0

ns

ns

μ

s

μ

s

MHz

0.05

0.05

5.0

10

Slave Serial Mode Programming Switching Characteristics

Notes: 1. The max limit of CCLK Low time is caused by dynamic circuitry inside the LCA device.

2. Configuration must be delayed until the INIT of all LCA devices is High.

3. At power-up, V

CC

must rise from 2.0 V to V

CC

min in less than 25 ms. If this is not possible, configuration can be de-

layed by holding RESET Low until V

CC

has reached 4.0 V (2.5 V for the XC3000L). A very long V

CC

rise time of >100

ms, or a non-monotonically rising V

CC

may require a >6-

μ

s High level on RESET, followed by a >6-

μ

s Low level on

RESET and D/P after V

CC

has reached 4.0 V (2.5 V for the XC3000L).

Description

RTRIG High

Symbol

Min

250

Max

Units

ns

RTRIG

1

T

RTH

CCLK

RTRIG setup

RDATA delay

High time

Low time

2

3

5

4

T

RTCC

T

CCRD

T

CCHR

T

CCLR

200

ns

ns

μ

s

μ

s

100

0.5

0.5

5

Notes: 1. During Readback, CCLK frequency may not exceed 1 MHz.

2. RETRIG (M0 positive transition) shall not be done until after one clock following active I/O pins.

3. Readback should not be initiated until configuration is complete.

4. T

CCLR

is 5

μ

s min to 15

μ

s max for XC3000L.

4 T

CCH

Bit n

Bit n + 1

Bit n

Bit n - 1

3 T

CCO

5 T

CCL

2 T

CCD

1 T

DCC

DIN

CCLK

DOUT

(Output)

X5379

1 T

RTH

5

3

4

4

2

T

CCL

T

CCRD

T

CCL

T

RTCC

DONE/PROG

(OUTPUT)

X6116

RTRIG (M0)

CCLK(1)

VALID

READBACK OUTPUT

H1-Z

VALID

READBACK OUTPUT

M1 Input/

RDATA Output

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC3142A-3TQ144I | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3042A-7TQ144C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3042A-7TQ144I | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3164A-3PC84I | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3164A-3PQ160C | Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC3042A-7PC84I0100 | 制造商:Xilinx 功能描述: |

| XC3042A-7PC84I090 | 制造商:Xilinx 功能描述: |

| XC3042A-7PCG84C | 制造商:Xilinx 功能描述:CMOS FPGA SMD 3042 PLCC84 5.25V |

| XC3042A-7PG132C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Field Programmable Gate Arrays (XC3000A/L, XC3100A/L) |

| XC3042A-7PG132I | 制造商:Xilinx 功能描述: |

發(fā)布緊急采購,3分鐘左右您將得到回復。