- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374975 > XC2V500 (Xilinx, Inc.) Virtex-II 1.5V Field-Programmable Gate Arrays PDF資料下載

參數(shù)資料

| 型號(hào): | XC2V500 |

| 廠商: | Xilinx, Inc. |

| 英文描述: | Virtex-II 1.5V Field-Programmable Gate Arrays |

| 中文描述: | 的Virtex - II 1.5V的現(xiàn)場(chǎng)可編程門陣列 |

| 文件頁數(shù): | 5/7頁 |

| 文件大小: | 127K |

| 代理商: | XC2V500 |

Virtex-II 1.5V Field-Programmable Gate Arrays

R

DS031-1 (v1.7) October 2, 2001

Advance Product Specification

1-800-255-7778Module 1 of 4

5

Boundary Scan

Boundary scan instructions and associated data registers

support a standard methodology for accessing and config-

uring Virtex-II devices that complies with IEEE standards

1149.1 - 1993 and 1532. A system mode and a test mode

are implemented. In system mode, a Virtex-II device per-

forms its intended mission even while executing non-test

boundary-scan instructions. In test mode, boundary-scan

test instructions control the I/O pins for testing purposes.

The Virtex-II Test Access Port (TAP) supports BYPASS,

PRELOAD, SAMPLE, IDCODE, and USERCODE non-test

instructions. The EXTEST, INTEST, and HIGHZ test instruc-

tions are also supported.

Configuration

Virtex-II devices are configured by loading data into internal

configuration memory, using the following five modes:

Slave-serial mode

Master-serial mode

Slave SelectMAP mode

Master SelectMAP mode

Boundary-Scan mode (IEEE 1532)

A Data Encryption Standard (DES) decryptor is available

on-chip to secure the bitstreams. One or two triple-DES key

sets can be used to optionally encrypt the configuration

information.

Readback and Integrated Logic Analyzer

Configuration data stored in Virtex-II configuration memory

can be read back for verification. Along with the configura-

tion data, the contents of all flip-flops/latches, distributed

SelectRAM, and block SelectRAM memory resources can

be read back. This capability is useful for real-time debug-

ging.

The Integrated Logic Analyzer (ILA) core and software pro-

vides a complete solution for accessing and verifying

Virtex-II devices.

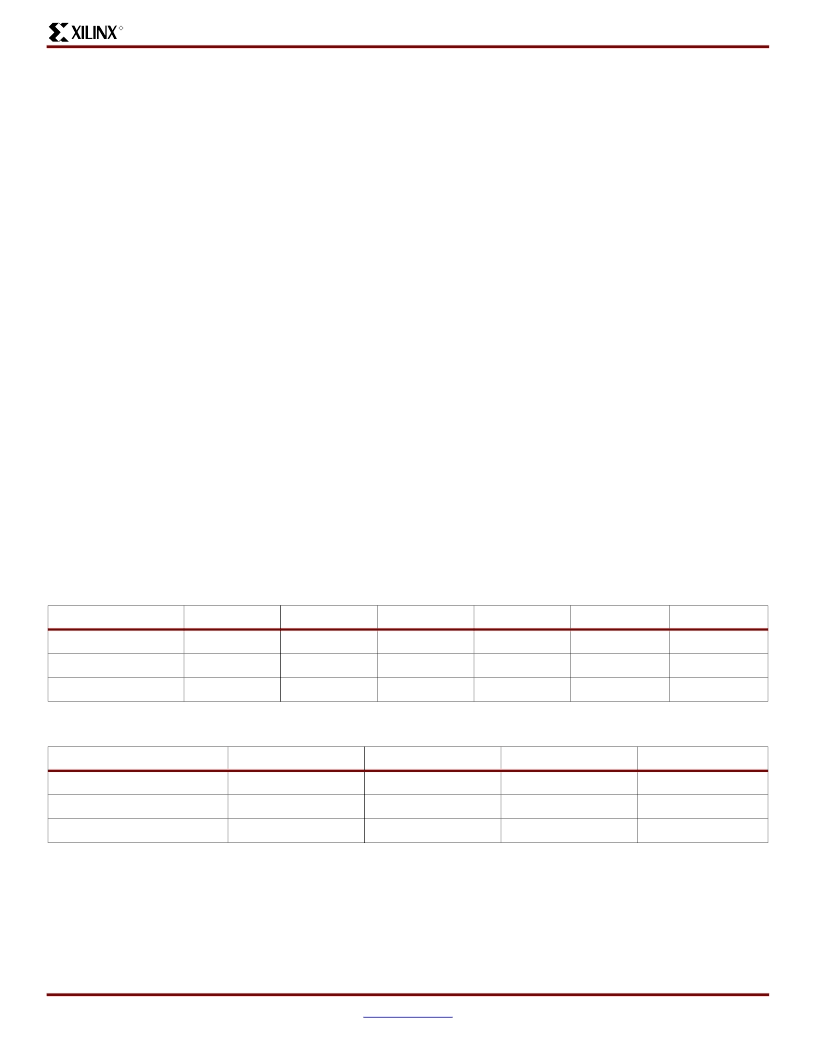

Virtex-II Device/Package Combinations

and Maximum I/O

Wire-bond and flip-chip packages are available.

Table 4

and

Table 5

show the maximum possible number of user I/Os in

wire-bond and flip-chip packages, respectively.

Table 6

shows the number of available user I/Os for all device/pack-

age combinations.

CS denotes wire-bond chip-scale ball grid array (BGA)

(0.80 mm pitch).

FG denotes wire-bond fine-pitch BGA (1.00 mm pitch).

FF denotes flip-chip fine-pitch BGA (1.00 mm pitch).

BG denotes standard BGA (1.27 mm pitch).

BF denotes flip-chip BGA (1.27 mm pitch).

The number of I/Os per package include all user I/Os except

the 15 control pins (CCLK, DONE, M0, M1, M2, PROG_B,

PWRDWN_B, TCK, TDI, TDO, TMS, HSWAP_EN, DXN,

DXP, AND RSVD) and VBATT.

Table 4:

Wire-Bond Packages Information

Package

CS144

FG256

FG456

FG676

BG575

BG728

Pitch (mm)

0.80

1.00

1.00

1.00

1.27

1.27

Size (mm)

12 x 12

17 x 17

23 x 23

27 x 27

31 x 31

35 x 35

I/Os

92

172

324

484

408

516

Table 5:

Flip-Chip Packages Information

Package

FF896

FF1152

FF1517

BF957

Pitch (mm)

1.00

1.00

1.00

1.27

Size (mm)

31 x 31

35 x 35

40 x 40

40 x 40

I/Os

624

824

1,108

684

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| XC2V4000-4FF1152I | Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V2000-5FG676I | Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V2000-4BG575I | Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V2000-5BG575I | Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V500-4FG256C | Virtex-II 1.5V Field-Programmable Gate Arrays |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| XC2V500-4BF957C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V500-4BF957I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V500-4BG575C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V500-4BG575I | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-II 1.5V Field-Programmable Gate Arrays |

| XC2V500-4BG728C | 制造商:XILINX 制造商全稱:XILINX 功能描述:Virtex-II 1.5V Field-Programmable Gate Arrays |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。