- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄44222 > LM1301-9PD0AH 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE PDF資料下載

參數(shù)資料

| 型號: | LM1301-9PD0AH |

| 元件分類: | 電源模塊 |

| 英文描述: | 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE |

| 封裝: | METAL, CASE M02, MODULE |

| 文件頁數(shù): | 4/25頁 |

| 文件大?。?/td> | 569K |

| 代理商: | LM1301-9PD0AH |

Cassette Style

DC-DC Converters

M Series

Edition 01/01.2001

12/25

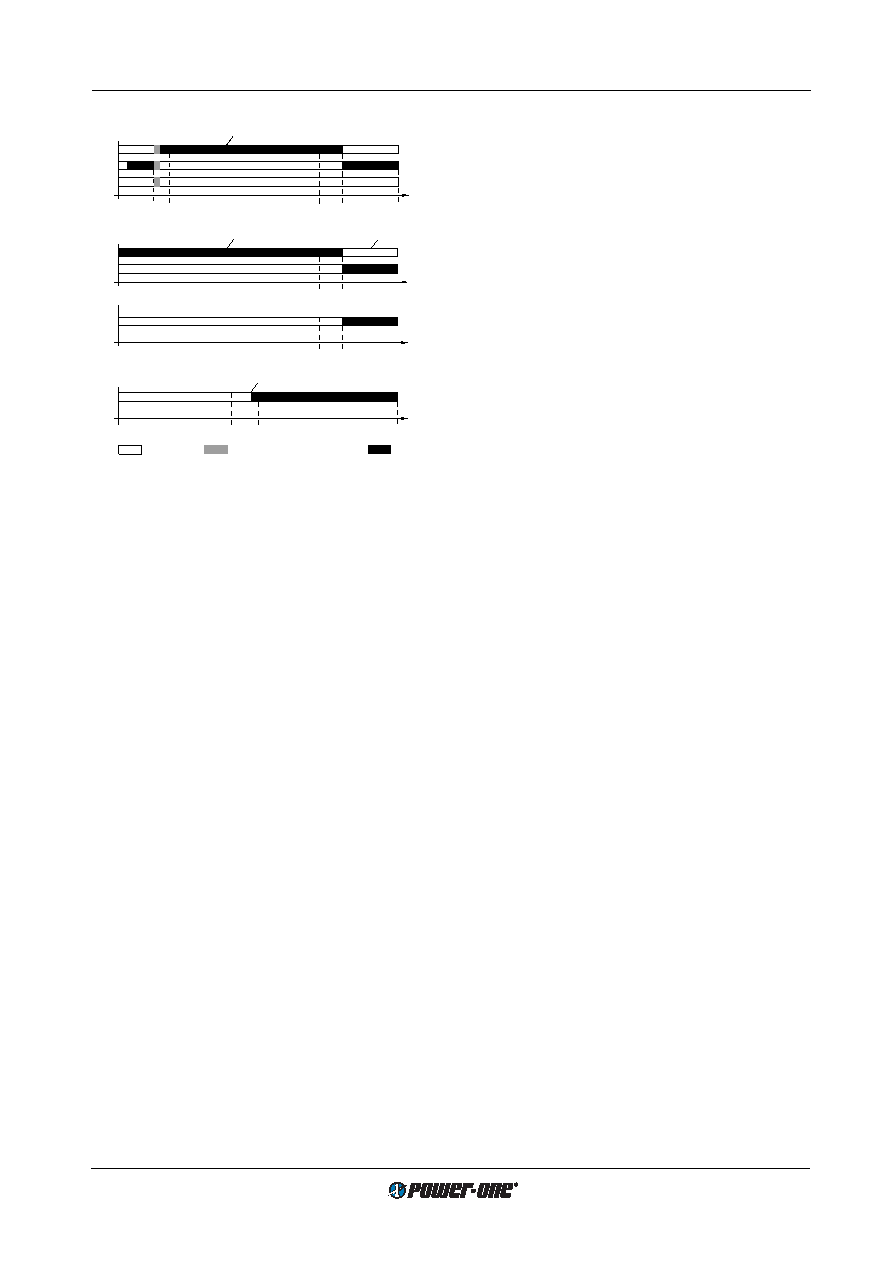

Display Status of LEDs

Uo1 > 0.95...0.98Uo1 adj

Ui max Ui ov

Ui min

Ui uv

Ui

Ui abs

OK

i

Uo1 > 0.95...0.98Uo1 adj

Io nom

IoL

Io

OK

Io L

Uo1 < 0.95...0.98Uo1 adj

TC

i

TC max

TPTC threshold

Ui inh

i

+50 V

+0.8 V

+2.4 V

-50 V

Uinh threshold

Io L

LED off

LED on

LED Status undefined

06002

Fig. 13

LEDs "OK" and "i" status versus input voltage

Conditions: Io

≤ I

o nom, TC

≤ T

C max, Uinh

≤ 0.8 V

Ui uv = undervoltage lock-out, Ui ov = overvoltage lock-out

LED "OK" and "Io L"status versus output current

Conditions: Ui min...Ui max, TC ≤ TC max, Uinh ≤ 0.8 V

LED "i"versus case temperature

Conditions: Ui min...Ui max, Io

≤ I

o nom, U inh

≤ 0.8 V

LED "i"versus Uinh

Conditions: Ui min...Ui max, Io

≤ I

o nom, TC

≤ T

C max

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| LM1301-9PD1AH | 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE |

| LM1501-7EPD3 | 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE |

| LM1501-7EPD9HF | 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE |

| LM1501-7EPD9H | 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE |

| LM1501-7EPV2AHF | 1-OUTPUT 50 W AC-DC REG PWR SUPPLY MODULE |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| LM1301-9R | 制造商:Power-One 功能描述:AC/DC Power Supply Single-OUT 12V 4A 50W 11-Pin 制造商:Power-One 功能描述:LM Series 50W Single Output 12V AC/DC Power Supply |

| LM13080N/A+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Voltage-Feedback Operational Amplifier |

| LM13080N/B+ | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Voltage-Feedback Operational Amplifier |

| LM130A-12C318 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Sunlight Readable 12.1 LCD Module |

| LM130SS1T611 | 制造商:SHARP 制造商全稱:Sharp Electrionic Components 功能描述:Color STN-LCD Module |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。