- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374934 > ST2202 (Electronic Theatre Controls, Inc.) 8 BIT Integrated Microcontroller with 256K Bytes ROM PDF資料下載

參數(shù)資料

| 型號(hào): | ST2202 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | 8 BIT Integrated Microcontroller with 256K Bytes ROM |

| 中文描述: | 8位微控制器集成256K字節(jié)ROM的 |

| 文件頁(yè)數(shù): | 51/65頁(yè) |

| 文件大?。?/td> | 1946K |

| 代理商: | ST2202 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)當(dāng)前第51頁(yè)第52頁(yè)第53頁(yè)第54頁(yè)第55頁(yè)第56頁(yè)第57頁(yè)第58頁(yè)第59頁(yè)第60頁(yè)第61頁(yè)第62頁(yè)第63頁(yè)第64頁(yè)第65頁(yè)

Sitronix

ST2202

Ver 2.0a

51/65

2003-May-05

B

S

1

2

3

4

5

6

B

P

S

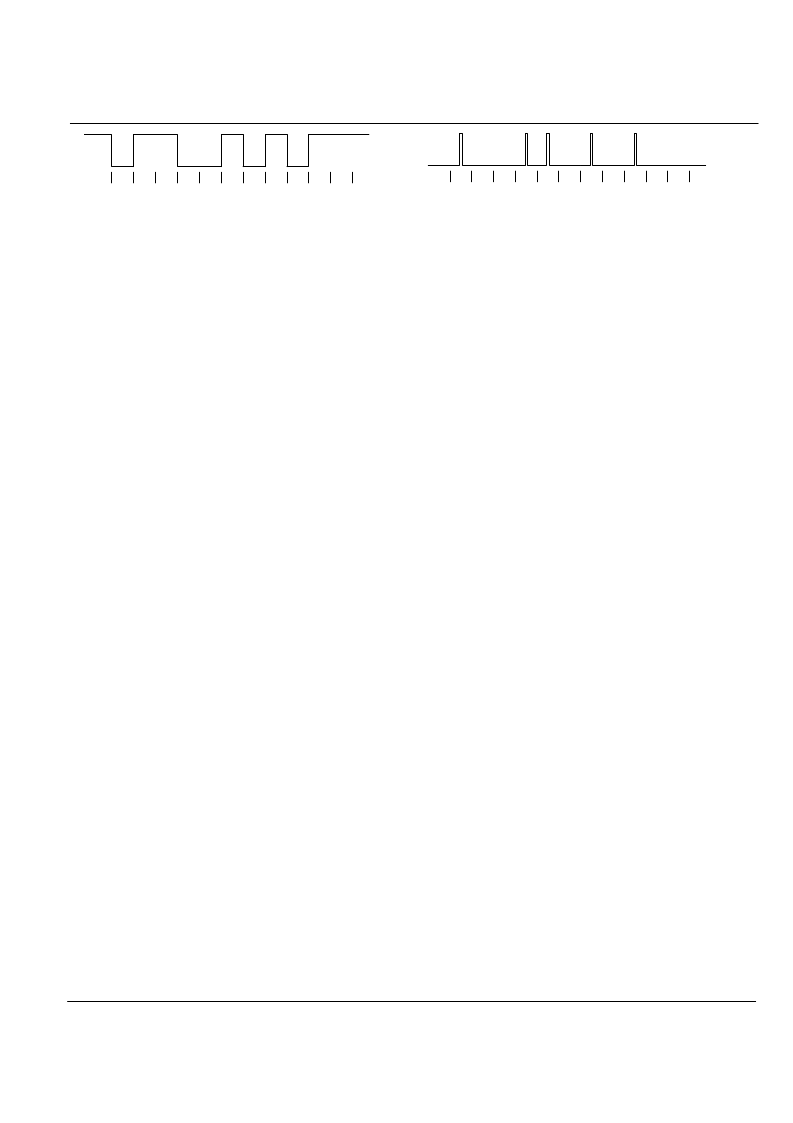

FIGURE 18-2 NRZ ASCII “S” with Odd Parity

B

S

1

2

3

4

5

6

B

P

S

FIGURE 18-3 IrDA ASCII “S” with Odd Parity

Two kinds of character, 7-bit and 8-bit, are supported by

ST2202. This is controlled by mode selection bit

UMOD

(

UCTR[1]

). Parity options are controlled by parity enable bit

18.2.3 Transmitter Operation

Transmitter operation is controlled by control bit

TXEN

(

USTR[0]

). The transmitter accepts a character from the

CPU bus, and then transmits it immediately after triggered

by writing “1” to control bit

TXTRG

(

USTR[1]

). When a

character is available for transmission, the start, stop, and

parity (if enabled) bits are added into the character, and

then it is serially shifted (LSB first) at the selected bit rate.

While transmitter is busy, the busy status is reported at

TXBZ

(

USTR[1]

) with logic value “1”. After all data bits are

18.2.4 Receiver Operation

Receiver operation is controlled by control bit

RXEN

(

USTR[2]

). Once the receiver is enabled, it searches for a

start bit, qualifies it, and then samples the succeeding data

bits at the perceived bit center. Jitter tolerance and noise

immunity are provided by sampling 16 times per bit and

using a voting circuit to enhance sampling. While receiving,

the busy status of receiver can be read from

RXBZ

(

USTR[3]

) with logic level “1”.

Receiving activity will be complete after the stop bit is

detected. Then

IRURX

(

IREQ[11]

) will be set to issue the

interrupt request. The received data can be obtained by

reading data register

UDATA

. Then the receive trigger bit

RXTRG

(

USTR[3]

) should be set to indicate that the data

register can be overwrote next time.

Three kinds of errors may arise from illegal received data,

which are reported at 3 bits of status register

USTR[6:4]

and are discussed below.

18.3 Interface Signals

PEN

(

UCTR[3]

) and parity mode selection bit

PMOD

(

UCTR[2]

). Other operations for transmitter and receiver

are described below.

finished,

IRUTX

(

IREQ[10]

) will be set to issue the interrupt

request. Next data transmission may continue with setting

trigger bit

TXTRG

again.

If the transmit buffer is empty, the transmitter outputs a

continuous idle (which is “1” for normal polarity). Moreover

a continuous “0” can also be outputted as a break character

by setting

BRK

bit (

UCTR[0]

) and then set the trigger bit.

.

1. Buffer Overrun Error

This error indicates that the receive trigger bit was not set

and the receiver overwrote data in receive buffer, i.e., the

previous character was lost. This also means the software

is not keeping up with the incoming data rate. Error is

updated and reported by reading

OER

(

USTR[4]

) for

current received character.

2. Parity Error

If parity is enabled, the parity bit of current received

character is checked and the status is updated in register

bit

PER

(

USTR[5]

).

3. Framing Error

This error indicates that a framing error is detected and

there may be corrupted data with missing stop bit. Error is

updated and reported by reading

FER

(

USTR[6]

) for current

received character.

Two sets of data lines can be enabled simultaneously for

communication, TXD0(PC6), RXD0(PC7) and the auxiliary

pins TXD1(PD6), RXD1(PD7). Data can inputs and outputs

from and to these pins. With setting related bits of port

function select registers (

PFC

and

PFD

), signals of the

external devices can be connected. Data in and from these

communication I/Os can be inverted by setting polarity

control bit

RXINV

and

TXINV

(

IRCTR[7:6]

). Direction

settings and function select bits should be ascertained

before using signals. Refer to section 9 for these settings.

The UART transmit data signal is output to one or both of

these two pins, which are multiplexed with PC6 and PD6.

These pins connect to standard RS-232 or infrared

transceiver modules.

RXD0 (PC7)/RXD1 (PD7)

The UART receive data signal is input from one or both of

these two pins, which are multiplexed with PC7 and PD7. If

RXD0 and RXD1 are enabled at a time, both signals will be

gated with AND logic to produce one single signal. These

TXD0 (PC6)/TXD1 (PD6)

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ST2221C | 16 BIT CONSTANT CURRENT LED DRIVERS |

| ST2225A-SS3 | LED DISPLAY DRIVER |

| ST2225A | LED DISPLAY DRIVER |

| ST2225A-D | LED DISPLAY DRIVER |

| st302 | PHOTOTRANSISTORS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ST2202A | 制造商:SITRONIX 制造商全稱:SITRONIX 功能描述:8 BIT Integrated Microcontroller with 256K Bytes ROM |

| ST2203U | 制造商:SITRONIX 制造商全稱:SITRONIX 功能描述:8-Bit Microcontroller With 2K Bytes RAM |

| ST2204 | 制造商:SITRONIX 制造商全稱:SITRONIX 功能描述:8 BIT Integrated Microcontroller with 512K Bytes ROM |

| ST220-50T2KI | 功能描述:鉭質(zhì)電容器-濕式 ST220-50T2KI RoHS:否 制造商:Vishay/Tansitor 電容:2800 uF 電壓額定值:35 V ESR:0.35 Ohms 容差:20 % 端接類型:Axial 工作溫度范圍:- 55 C to + 85 C 制造商庫(kù)存號(hào):T4 Case 外殼直徑:9.52 mm 外殼長(zhǎng)度:26.97 mm 外殼寬度: 外殼高度: 系列:STE 產(chǎn)品:Tantalum Wet Hermetically Sealed 封裝:Bulk |

| ST220-50T2MI | 功能描述:鉭質(zhì)電容器-濕式 220UF 50V 20% T2 RoHS:否 制造商:Vishay/Tansitor 電容:2800 uF 電壓額定值:35 V ESR:0.35 Ohms 容差:20 % 端接類型:Axial 工作溫度范圍:- 55 C to + 85 C 制造商庫(kù)存號(hào):T4 Case 外殼直徑:9.52 mm 外殼長(zhǎng)度:26.97 mm 外殼寬度: 外殼高度: 系列:STE 產(chǎn)品:Tantalum Wet Hermetically Sealed 封裝:Bulk |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。