- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374929 > SSD1905QT2 (Electronic Theatre Controls, Inc.) LCD Graphics Controller CMOS PDF資料下載

參數(shù)資料

| 型號: | SSD1905QT2 |

| 廠商: | Electronic Theatre Controls, Inc. |

| 英文描述: | LCD Graphics Controller CMOS |

| 中文描述: | LCD圖形控制器的CMOS |

| 文件頁數(shù): | 151/153頁 |

| 文件大?。?/td> | 863K |

| 代理商: | SSD1905QT2 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁第146頁第147頁第148頁第149頁第150頁當前第151頁第152頁第153頁

SOLOMON

Rev 1.3

10/2002

SSD1905

142

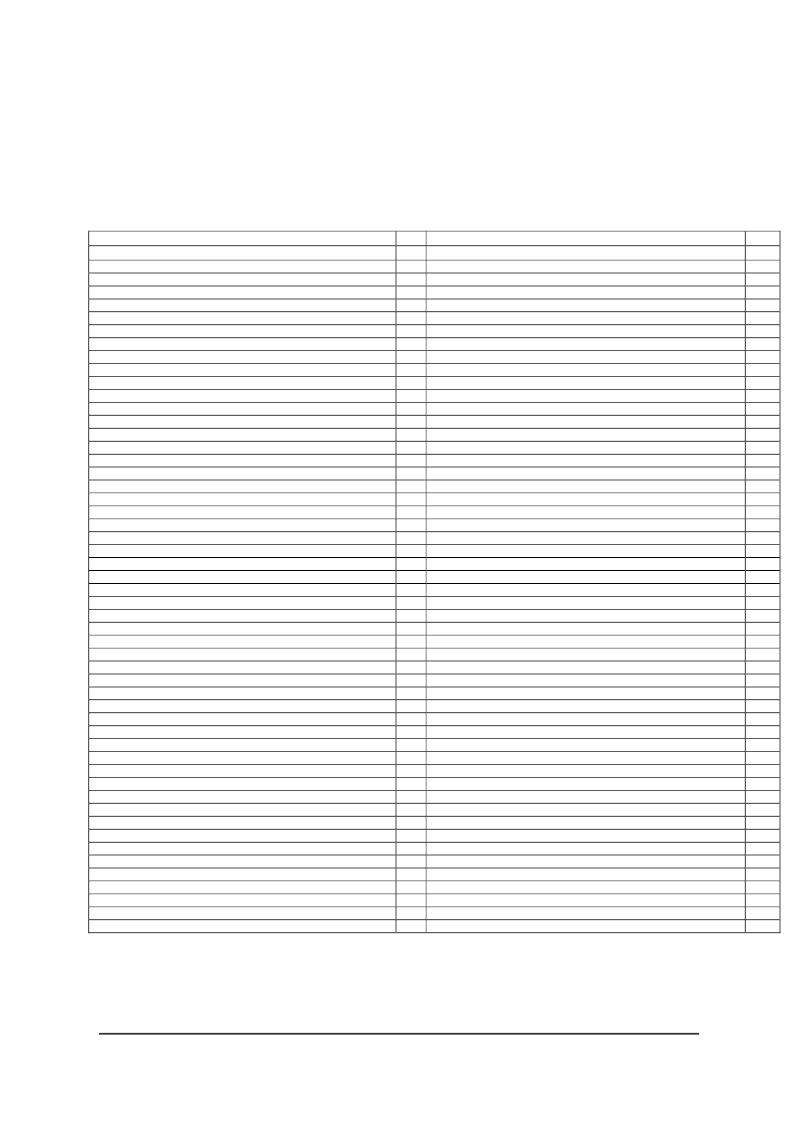

22.2 Register Table

Table 22-1 : SSD1905 Register Table (1 of 2)

Register

Read-Only Configuration Registers

REG[01h] Display Buffer Size Register

REG[02h] Configuration Readback Register

REG[03h] Product / Revision Code Register

Clock Configuration Registers

REG[04h] Memory Clock Configuration Register

REG[05h] Pixel Clock Configuration Register

Look-Up Table Registers

REG[08h] Look-Up Table Blue Write Data Register

REG[09h] Look-Up Table Green Write Data Register

REG[0Ah] Look-Up Table Red Write Data Register

REG[0Bh] Look-Up Table Write Address Register

REG[0Ch] Look-Up Table Blue Read Data Register

REG[0Dh] Look-Up Table Green Read Data Register

REG[0Eh] Look-Up Table Red Read Data Register

REG[0Fh] Look-Up Table Read Address Register

Panel Configuration Registers

REG[10h] Panel Type Register

REG[11h] MOD Rate Register

REG[12h] Horizontal Total Register

REG[14h] Horizontal Display Period Register

REG[16h] Horizontal Display Period Start Position Register 0

REG[17h] Horizontal Display Period Start Position Register 1

REG[18h] Vertical Total Register 0

REG[19h] Vertical Total Register 1

REG[1Ch] Vertical Display Period Register 0

REG[1Dh] Vertical Display Period Register 1

REG[1Eh] Vertical Display Period Start Position Register 0

REG[1Fh] Vertical Display Period Start Position Register 1

REG[20h] LLINE Pulse Width Register

REG[22h] LLINE Pulse Start Position Register 0

REG[23h] LLINE Pulse Start Position Register 1

REG[24h] LFRAME Pulse Width Register

REG[26h] LFRAME Pulse Start Position Register 0

REG[27h] LFRAME Pulse Start Position Register 1

REG[30h] LFRAME Pulse Start Offset Register 0

REG[31h] LFRAME Pulse Start Offset Register 1

REG[34h] LFRAME Pulse Stop Offset Register 0

REG[35h] LFRAME Pulse Stop Offset Register 1

REG[38h] HR-TFT Special Output Register

REG[3Ch] GPIO0 Pulse Start Register

REG[3Eh] GPIO0 Pulse Stop Register

REG[40h] GPIO2 Pulse Delay Register

REG[45h] STN Color Depth Control Register

REG[50h] Dynamic Dithering Control Register

Display Mode Registers

REG[70h] Display Mode Register

REG[71h] Special Effects Register

REG[74h] Main Window Display Start Address Register 0

REG[75h] Main Window Display Start Address Register 1

REG[76h] Main Window Display Start Address Register 2

REG[78h] Main Window Line Address Offset Register 0

REG[79h] Main Window Line Address Offset Register 1

Pg

15

15

16

16

16

17

18

18

19

19

19

20

20

21

22

22

23

23

23

23

24

24

24

25

25

25

26

26

26

27

27

27

27

28

28

28

29

29

30

30

31

31

33

34

34

35

35

35

Register

Floating Window Registers

REG[7Ch] Floating Window Display Start Address Register 0

REG[7Dh] Floating Window Display Start Address Register 1

REG[7Eh] Floating Window Display Start Address Register 2

REG[80h] Floating Window Line Address Offset Register 0

REG[81h] Floating Window Line Address Offset Register 1

REG[84h] Floating Window Start Position X Register 0

REG[85h] Floating Window Start Position X Register 1

REG[88h] Floating Window Start Position Y Register 0

REG[89h] Floating Window Start Position Y Register 1

REG[8Ch] Floating Window End Position X Register 0

REG[8Dh] Floating Window End Position X Register 1

REG[90h] Floating Window End Position Y Register 0

REG[91h] Floating Window End Position Y Register 1

Miscellaneous Registers

REG[A0h] Power Saving Configuration Register

REG[A2h] Software Reset Register

REG[A4h] Scratch Pad Register 0

REG[A5h] Scratch Pad Register 1

General Purpose IO Pins Registers

REG[A8h] General Purpose IO Pins Configuration Register 0

REG[A9h] General Purpose IO Pins Configuration Register 1

REG[ACh] General Purpose IO Pins Status/Control Register 0

REG[ADh] General Purpose IO Pins Status/Control Register 1

PWM Clock and CV Pulse Configuration Registers

REG[B0h] PWM Clock / CV Pulse Control Register

REG[B1h] PWM Clock / CV Pulse Configuration Register

REG[B2h] CV Pulse Burst Length Register

REG[B3h] PWM Duty Cycle Register

Pg

36

36

36

37

37

37

38

38

39

39

40

40

41

41

42

42

42

43

44

44

45

46

47

48

48

相關PDF資料 |

PDF描述 |

|---|---|

| SSF-LXH100GD-01 | T-5mm (T-1 3/4) LED, RIGHT ANGLE FAULT INDICATOR, 565nm GREEN LED, GREEN DIFFUSED LENS |

| SSI-LXH8080SRD | SSI-LXH8080SRD |

| SSI204 | 5V LOW POWER DTMF RECEIVER |

| SSI32F8030 | Programmable Electronic Filter |

| SSI75T201 | INTEGRATED DTMF RECEIVER |

相關代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SSD1906 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:256K Embedded Display SRAM LCD Graphic Controller CMOS |

| SSD1906QT2 | 制造商: 功能描述: 制造商:undefined 功能描述: |

| SSD1926 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:JPEG壓縮編碼的SD接口256K的SRAM嵌入式顯示器圖像處理器的CMOS |

| SSD1D40 | 制造商:M.E.C. Relays 功能描述: |

| SSD2 | 功能描述:保險絲 2A 240VAC IND RoHS:否 制造商:Littelfuse 產(chǎn)品:Surface Mount Fuses 電流額定值:0.5 A 電壓額定值:600 V 保險絲類型:Fast Acting 保險絲大小/組:Nano 尺寸:12.1 mm L x 4.5 mm W 安裝風格: 端接類型:SMD/SMT 系列:485 |

發(fā)布緊急采購,3分鐘左右您將得到回復。