- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374854 > SN74LS162N (Motorola, Inc.) High Performance Optical Mouse Sensor (Optimized For Gaming And Office Environments) PDF資料下載

參數(shù)資料

| 型號(hào): | SN74LS162N |

| 廠商: | Motorola, Inc. |

| 英文描述: | High Performance Optical Mouse Sensor (Optimized For Gaming And Office Environments) |

| 中文描述: | BCD碼十年計(jì)數(shù)器/ 4位二進(jìn)制計(jì)數(shù)器 |

| 文件頁(yè)數(shù): | 5/6頁(yè) |

| 文件大小: | 79K |

| 代理商: | SN74LS162N |

5-5

FAST AND LS TTL DATA

SN54/74LS160A

SN54/74LS161A

SN54/74LS162A

SN54/74LS163A

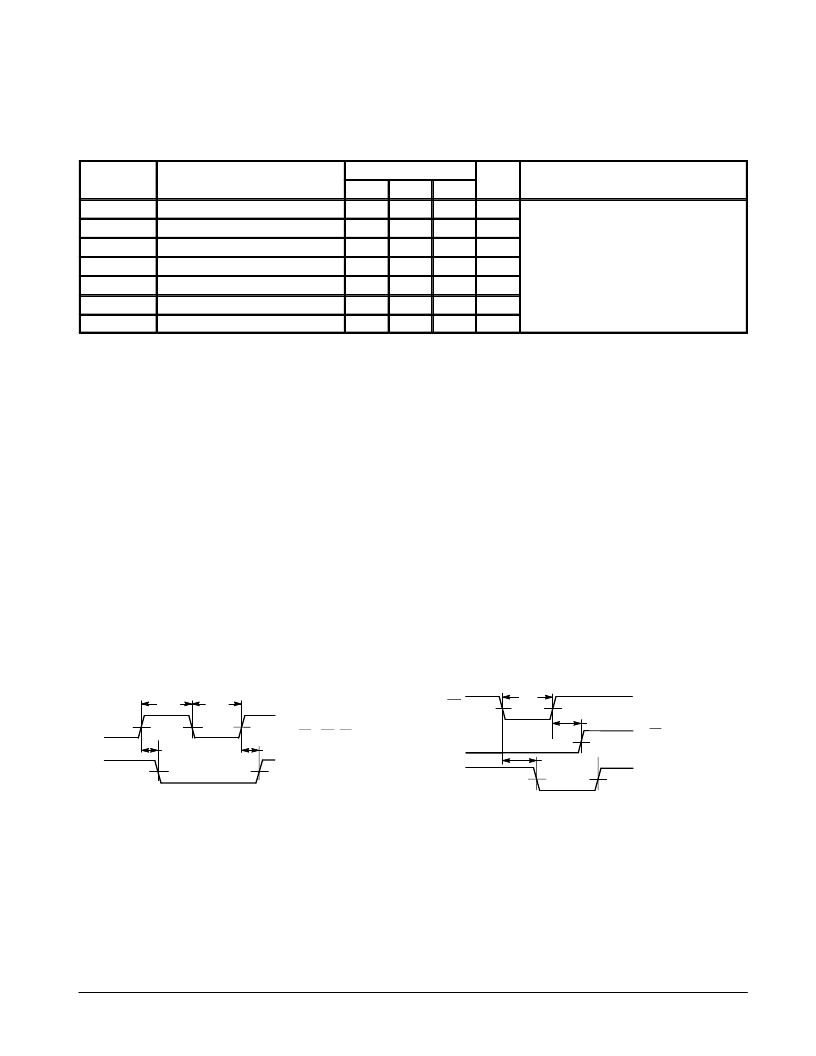

AC SETUP REQUIREMENTS

(TA = 25

°

C)

Symbol

b l

Parameter

Limits

U i

Unit

Test Conditions

di i

Min

Typ

Max

tWCP

tW

ts

ts

th

th

trec

*CEP, CET or DATA

Clock Pulse Width Low

25

ns

VCC = 5.0 V

5 0 V

5 0 V

5 0 V

MR or SR Pulse Width

20

ns

Setup Time, other*

20

ns

Setup Time PE or SR

25

ns

Hold Time, data

3

ns

Hold Time, other

0

ns

Recovery Time MR to CP

15

ns

DEFINITION OF TERMS

SETUP TIME (ts) — is defined as the minimum time required

for the correct logic level to be present at the logic input prior to

the clock transition from LOW to HIGH in order to be recog-

nized and transferred to the outputs.

HOLD TIME (th) — is defined as the minimum time following

the clock transition from LOW to HIGH that the logic level must

be maintained at the input in order to ensure continued recog-

nition. A negative HOLD TIME indicates that the correct logic

level may be released prior to the clock transition from LOW to

HIGH and still be recognized.

RECOVERY TIME (trec) — is defined as the minimum time re-

quired between the end of the reset pulse and the clock transi-

tion from LOW to HIGH in order to recognize and transfer

HIGH Data to the Q outputs.

AC WAVEFORMS

Figure 1. Clock to Output Delays, Count

Frequency, and Clock Pulse Width

Figure 2. Master Reset to Output Delay, Master Reset

Pulse Width, and Master Reset Recovery Time

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

1.3 V

CP

Q

tW(H)

tW(L)

trec

tPHL

tPHL

tPLH

OTHER CONDITIONS:

PE = MR (SR) = H

CEP = CET = H

OTHER CONDITIONS:

PE = L

P0 = P1 = P2 = P3 = H

tW

Q0

Q1

Q2

Q3

MR

CP

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54LS169J | BCD DECADE/MODULO 16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS |

| SN54LS168J | BCD DECADE/MODULO 16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS |

| SN74LS168D | Low Noise, High Linearity Active Bias Amplifier |

| SN74LS168N | Low Noise Amplifier with Bypass Switch |

| SN74LS169D | BCD DECADE/MODULO 16 BINARY SYNCHRONOUS BI-DIRECTIONAL COUNTERS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74LS163AD | 功能描述:計(jì)數(shù)器 IC 4-Bit Synchronous Binary Counters RoHS:否 制造商:NXP Semiconductors 計(jì)數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計(jì)數(shù)法: 計(jì)數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| SN74LS163ADE4 | 功能描述:計(jì)數(shù)器 IC 4-Bit Synchronous Binary Counters RoHS:否 制造商:NXP Semiconductors 計(jì)數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計(jì)數(shù)法: 計(jì)數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| SN74LS163ADG4 | 功能描述:計(jì)數(shù)器 IC Sync 4B Binary Counters RoHS:否 制造商:NXP Semiconductors 計(jì)數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計(jì)數(shù)法: 計(jì)數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| SN74LS163ADR | 功能描述:計(jì)數(shù)器 IC 4-Bit Synchronous Binary Counters RoHS:否 制造商:NXP Semiconductors 計(jì)數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計(jì)數(shù)法: 計(jì)數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

| SN74LS163ADRE4 | 功能描述:計(jì)數(shù)器 IC 4-Bit Synchronous Binary Counters RoHS:否 制造商:NXP Semiconductors 計(jì)數(shù)器類型:Binary Counters 邏輯系列:74LV 位數(shù):10 計(jì)數(shù)法: 計(jì)數(shù)順序: 工作電源電壓:1 V to 5.5 V 工作溫度范圍:- 40 C to + 125 C 封裝 / 箱體:SOT-109 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。