- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374861 > SN74ACT3651PQ (Texas Instruments, Inc.) Low-Voltage CMOS Octal Transparent Latch; Package: TSSOP 20 LEAD; No of Pins: 20; Container: Tape and Reel; Qty per Container: 2500 PDF資料下載

參數(shù)資料

| 型號(hào): | SN74ACT3651PQ |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | Low-Voltage CMOS Octal Transparent Latch; Package: TSSOP 20 LEAD; No of Pins: 20; Container: Tape and Reel; Qty per Container: 2500 |

| 中文描述: | 2048】36時(shí)鐘先入先出存儲(chǔ)器 |

| 文件頁數(shù): | 11/26頁 |

| 文件大小: | 376K |

| 代理商: | SN74ACT3651PQ |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁

SN74ACT3651

2048

×

36

CLOCKED FIRST-IN, FIRST-OUT MEMORY

SCAS439D – JUNE 1994 – REVISED FEBRUARY 1999

11

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

mailbox registers

Two 36-bit bypass registers pass command and control information between port A and port B. The

mailbox-select (MBA, MBB) inputs choose between a mail register and a FIFO for a port data-transfer operation.

A low-to-high transition on CLKA writes A0–A35 data to the mail1 register when a port-A write is selected by

CSA, W/RA, and ENA with MBA high. A low-to-high transition on CLKB writes B0–B35 data to the mail2 register

when a port-B write is selected by CSB, W/RB, and ENB with MBB high. Writing data to a mail register sets its

corresponding flag (MBF1 or MBF2) low. Attempted writes to a mail register are ignored while its mail flag is

low.

When the port-B data (B0–B35) outputs are active, the data on the bus comes from the FIFO output register

when the MBB input is low and from the mail1 register when MBB is high. Mail2 data is always present on the

port-A data (A0–A35) outputs when they are active. The mail1 register flag (MBF1) is set high by a low-to-high

transition on CLKB when a port-B read is selected by CSB, W/RB, and ENB with MBB high. The mail2 register

flag (MBF2) is set high by a low-to-high transition on CLKA when a port-A read is selected by CSA, W/RA, and

ENA with MBA high. The data in a mail register remains intact after it is read and changes only when new data

is written to the register.

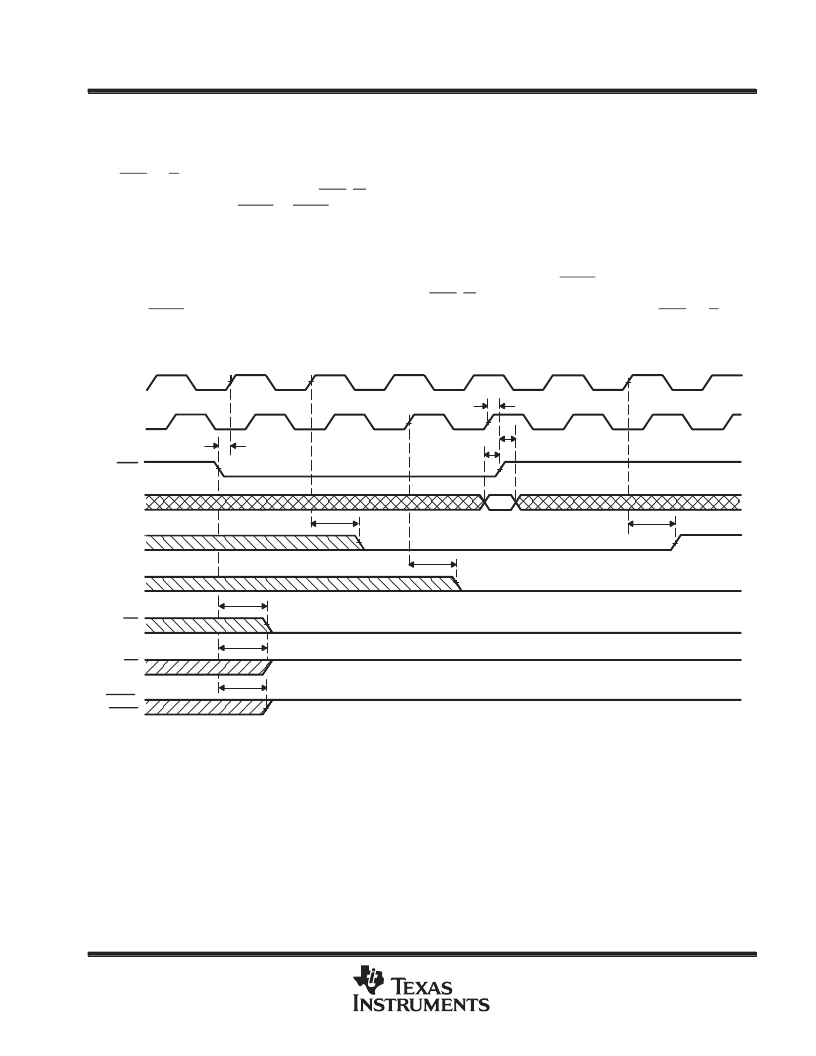

tpd(R-F)

tpd(C-IR)

CLKA

CLKB

RST

0,1

th(FS)

tsu(FS)

th(RS)

tsu(RS)

FS1, FS0

IR

tpd(C-IR)

ììììììììììì

OR

tpd(C-OR)

ìììììììììììììììì

tpd(R-F)

AE

AF

ììììììì

MBF1,

MBF2

tpd(R-F)

Figure 1. FIFO Reset Loading X and Y With a Preset Value of Eight

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN74ACT373DB | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

| SN54ACT373FK | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

| SN54ACT373J | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

| SN54ACT373W | OCTAL D-TYPE TRANSPARENT LATCHES WITH 3-STATE OUTPUTS |

| SN74ACT374DB | OCTAL D-TYPE EDGE-TRIGGERED FLIP-FLOPS WITH 3-STATE OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN74ACT373DB | 制造商:Rochester Electronics LLC 功能描述:- Bulk |

| SN74ACT373DBR | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ACT373DBRE4 | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ACT373DBRG4 | 功能描述:閉鎖 Octal D-Type Transp RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

| SN74ACT373DW | 功能描述:閉鎖 Tri-St Octal D-Type RoHS:否 制造商:Micrel 電路數(shù)量:1 邏輯類型:CMOS 邏輯系列:TTL 極性:Non-Inverting 輸出線路數(shù)量:9 高電平輸出電流: 低電平輸出電流: 傳播延遲時(shí)間: 電源電壓-最大:12 V 電源電壓-最小:5 V 最大工作溫度:+ 85 C 最小工作溫度:- 40 C 封裝 / 箱體:SOIC-16 封裝:Reel |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。