- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374851 > SN54AS823AFK (Texas Instruments, Inc.) 9-BIT BUS-INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS PDF資料下載

參數(shù)資料

| 型號: | SN54AS823AFK |

| 廠商: | Texas Instruments, Inc. |

| 元件分類: | 通用總線功能 |

| 英文描述: | 9-BIT BUS-INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS |

| 中文描述: | 9位總線接口倒裝3觸發(fā)器態(tài)輸出 |

| 文件頁數(shù): | 1/7頁 |

| 文件大小: | 112K |

| 代理商: | SN54AS823AFK |

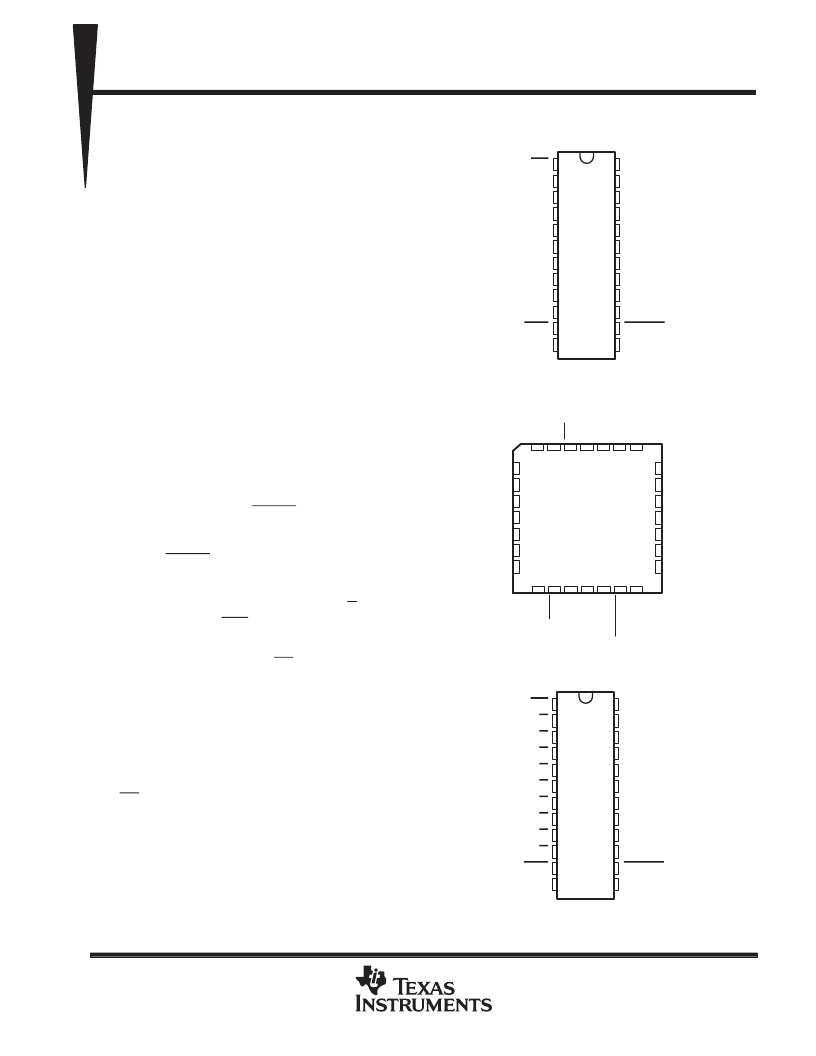

SN54AS823A . . . JT PACKAGE

SN74AS823A . . . DW OR NT PACKAGE

(TOP VIEW)

SN54AS823A . . . FK PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

OE

1D

2D

3D

4D

5D

6D

7D

8D

9D

CLR

GND

V

CC

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

9Q

CLKEN

CLK

NC – No internal connection

3 2 1 28 27

12 13

5

6

7

8

9

10

11

25

24

23

22

21

20

19

3Q

4Q

5Q

NC

6Q

7Q

8Q

3D

4D

5D

NC

6D

7D

8D

4

26

14 15 16 17 18

9

C

G

N

C

C

9

2

1

O

N

1

2

V

C

C

SN74AS824A . . . DW OR NT PACKAGE

(TOP VIEW)

1

2

3

4

5

6

7

8

9

10

11

12

24

23

22

21

20

19

18

17

16

15

14

13

OE

1D

2D

3D

4D

5D

6D

7D

8D

9D

CLR

GND

V

CC

1Q

2Q

3Q

4Q

5Q

6Q

7Q

8Q

9Q

CLKEN

CLK

SN54AS823A, SN74AS823A, SN74AS824A

9-BIT BUS-INTERFACE FLIP-FLOPS

WITH 3-STATE OUTPUTS

SDAS231A – JUNE 1984 – REVISED AUGUST 1995

Copyright

1995, Texas Instruments Incorporated

1

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

Functionally Equivalent to AMD’s AM29823

and AM29824

Provide Extra Data Width Necessary for

Wider Address/Data Paths or Buses With

Parity

Outputs Have Undershoot-Protection

Circuitry

Power-Up High-Impedance State

Buffered Control Inputs to Reduce

dc Loading Effects

Package Options Include Plastic

Small-Outline (DW) Packages, Ceramic

Chip Carriers (FK), and Standard Plastic

(NT) and Ceramic (JT) 300-mil DIPs

description

These 9-bit flip-flops feature 3-state outputs

designed specifically for driving highly capacitive

or relatively low-impedance loads. These devices

are particularly suitable for implementing wider

buffer registers, I/O ports, bidirectional bus

drivers, parity bus interfacing, and working

registers.

With the clock-enable (CLKEN) input low, the nine

D-type edge-triggered flip-flops enter data on the

low-to-high transitions of the clock (CLK) input.

Taking CLKEN high disables the clock buffer,

latching the outputs. The SN54AS823A and

SN74AS823A have noninverting data (D) inputs

and the SN74AS824A has inverting (D) inputs.

Taking the clear (CLR) input low causes the nine

Q outputs to go low independently of the clock.

A buffered output-enable (OE) input can be used

to place the nine outputs in either a normal logic

state (high or low logic level) or the high-

impedance state. In the high-impedance state, the

outputs neither load nor drive the bus lines

significantly. The high-impedance state and

increased drive provide the capability to drive bus

lines without interface or pullup components.

OE does not affect the internal operation of the

flip-flops. Old data can be retained or new data

can be entered while the outputs are in the

high-impedance state.

The SN54AS823A is characterized for operation

over the full military temperature range of –55

°

C

to 125

°

C. The SN74AS823A and SN74AS824A

are characterized for operation from 0

°

C to 70

°

C.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of Texas Instruments

standard warranty. Production processing does not necessarily include

testing of all parameters.

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54AS823AJT | 9-BIT BUS-INTERFACE FLIP-FLOPS WITH 3-STATE OUTPUTS |

| SN54AS885FK | 8-BIT MAGNITUDE COMPARATORS |

| SN54BCT125AFK | KPT 55C 55#20 SKT RECP |

| SN54BCT125AW | QUADRUPLE BUS BUFFER GATES WITH 3-STATE OUTPUTS |

| SN54BCT543FK | OCTAL REGISTERED TRANSCEIVERS WITH 3-STATE OUTPUTS |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN54AS825JT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel 制造商:Texas Instruments 功能描述: |

| SN54AS826JT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel 制造商:Texas Instruments 功能描述: |

| SN54AS869JT | 制造商:Texas Instruments 功能描述:SYNCHRONOUS 8-BIT UP/DOWN COUNTER - Rail/Tube |

| SN54AS873JT | 制造商:Rochester Electronics LLC 功能描述:- Tape and Reel |

| SN54BCT125AJ | 制造商:Texas Instruments 功能描述:Buffer/Line Driver 4-CH Non-Inverting 3-ST BiCMOS 14-Pin CDIP Tube 制造商:Texas Instruments 功能描述:BFFR/LINE DRVR 4-CH NON-INV 3-ST BICMOS 14CDIP - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。