- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374848 > SN54ABT8952 (Texas Instruments, Inc.) SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS PDF資料下載

參數(shù)資料

| 型號: | SN54ABT8952 |

| 廠商: | Texas Instruments, Inc. |

| 英文描述: | SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS |

| 中文描述: | 掃描測試設(shè)備與八進制注冊總線收發(fā)器 |

| 文件頁數(shù): | 8/24頁 |

| 文件大?。?/td> | 365K |

| 代理商: | SN54ABT8952 |

SN54ABT8952, SN74ABT8952

SCAN TEST DEVICES WITH

OCTAL REGISTERED BUS TRANSCEIVERS

SCBS121D – AUGUST 1992 – REVISED JULY 1996

8

POST OFFICE BOX 655303

DALLAS, TEXAS 75265

register overview

With the exception of the bypass register, any test register can be thought of as a serial-shift register with a

shadow latch on each bit. The bypass register differs in that it contains only a shift register. During the

appropriate capture state (Capture-IR for instruction register, Capture-DR for data registers), the shift register

can be parallel loaded from a source specified by the current instruction. During the appropriate shift state

(Shift-IR or Shift-DR), the contents of the shift register are shifted out from TDO while new contents are shifted

in at TDI. During the appropriate update state (Update-IR or Update-DR), the shadow latches are updated from

the shift register.

instruction register description

The instruction register (IR) is eight bits long and tells the device what instruction is to be executed. Information

contained in the instruction includes the mode of operation (either normal mode, in which the device performs

its normal logic function, or test mode, in which the normal logic function is inhibited or altered), the test operation

to be performed, which of the three data registers is to be selected for inclusion in the scan path during

data-register scans, and the source of data to be captured into the selected data register during Capture-DR.

Table 3 lists the instructions supported by the ’ABT8952. The even-parity feature specified for SCOPE

devices

is supported in this device. Bit 7 of the instruction opcode is the parity bit. Any instructions that are defined for

SCOPE

devices but are not supported by this device default to BYPASS.

During Capture-IR, the IR captures the binary value 10000001. As an instruction is shifted in, this value is shifted

out via TDO and can be inspected as verification that the IR is in the scan path. During Update-IR, the value

that has been shifted into the IR is loaded into shadow latches. At this time, the current instruction is updated,

and any specified mode change takes effect. At power up or in the Test-Logic-Reset state, the IR is reset to the

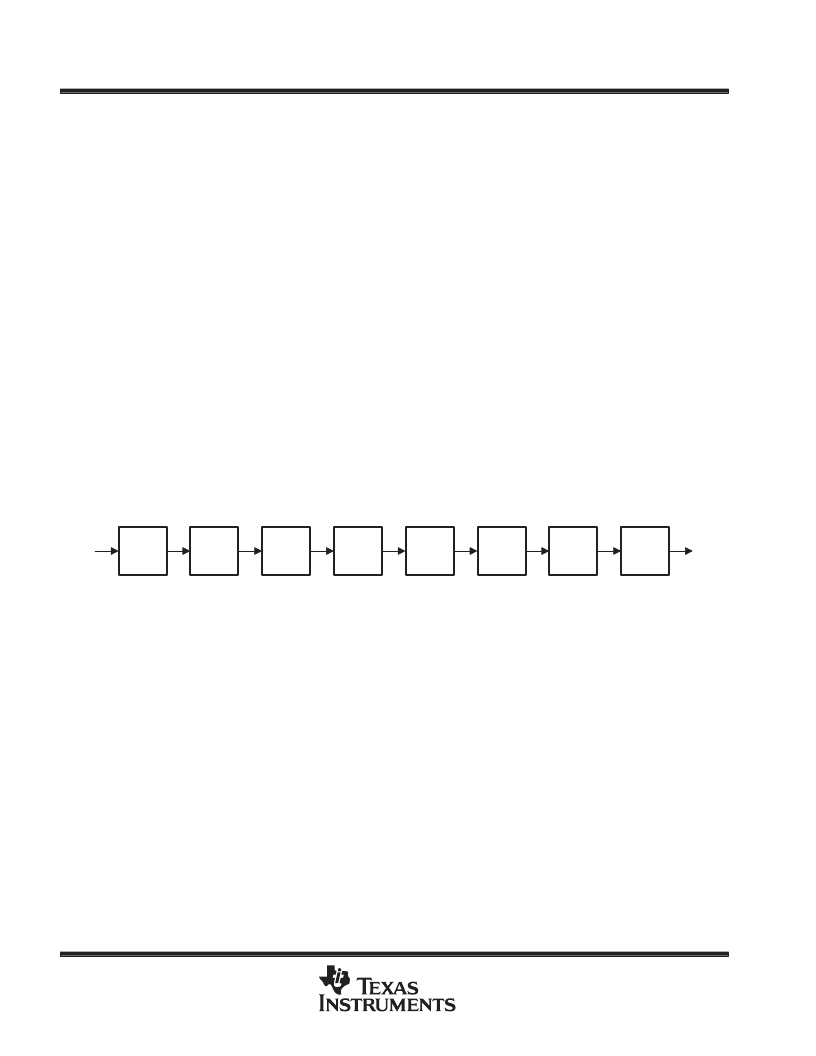

binary value 11111111, which selects the BYPASS instruction. The IR order of scan is shown in Figure 2.

Bit 6

Bit 5

Bit 4

Bit 3

Bit 2

Bit 1

TDO

TDI

Bit 7

Parity

(MSB)

Bit 0

(LSB)

Figure 2. Instruction Register Order of Scan

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SN54ABT8952FK | SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS |

| SN54ABT8952JT | SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS |

| SN54ABTE16245WD | 16-BIT INCIDENT-WAVE SWITCHING BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN74ABTE16245DGG | 16-BIT INCIDENT-WAVE SWITCHING BUS TRANSCEIVERS WITH 3-STATE OUTPUTS |

| SN54AC00FK | QUADRUPLE 2-INPUT POSITIVE-NAND GATES |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SN54ABT8952_07 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS |

| SN54ABT8952FK | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS |

| SN54ABT8952JT | 制造商:TI 制造商全稱:Texas Instruments 功能描述:SCAN TEST DEVICES WITH OCTAL REGISTERED BUS TRANSCEIVERS |

| SN54ABT8996 | 制造商:TI 制造商全稱:Texas Instruments 功能描述:10-BIT ADDRESSABLE SCAN PORTS MULTIDROP-ADDRESSABLE IEEE STD 1149.1 JTAG TAP TRANSCEIVERS |

| SN54ABT8996FK | 制造商:Texas Instruments 功能描述:ADDRESSABLE SCAN PORT 28LCCC - Rail/Tube |

發(fā)布緊急采購,3分鐘左右您將得到回復。