- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄374786 > SHARP_LH7A404 (Sharp Corporation) 32 BIT SYSTEM ON CHIP PDF資料下載

參數(shù)資料

| 型號(hào): | SHARP_LH7A404 |

| 廠商: | Sharp Corporation |

| 英文描述: | 32 BIT SYSTEM ON CHIP |

| 中文描述: | 32位片上系統(tǒng) |

| 文件頁(yè)數(shù): | 7/51頁(yè) |

| 文件大小: | 387K |

| 代理商: | SHARP_LH7A404 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)當(dāng)前第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)第49頁(yè)第50頁(yè)第51頁(yè)

32-Bit System-on-Chip

LH7A404

Advance Data Sheet

7

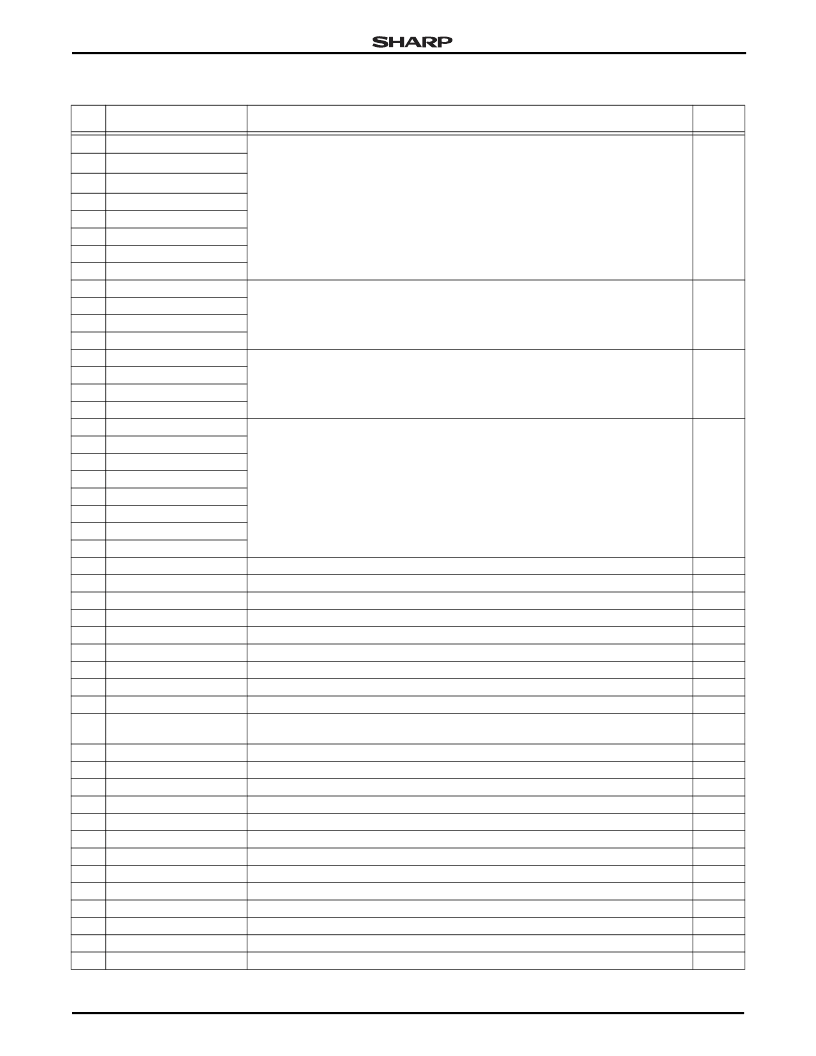

AB10 PD0/LCDVD8

GPIO Port D and LCD Video Data Interface

16 mA

AA10 PD1/LCDVD9

Y10

W10

AB11 PD4/LCDVD12

AA11 PD5/LCDVD13

Y11

PD6/LCDVD14

AB12 PD7/LCDVD15

AA8

PE0/LCDVD4

AA9

PE1/LCDVD5

Y9

PE2/LCDVD6

W9

PE3/LCDVD7

C4

PE4

A3

PE5

B3

PE6

A2

PE7

L13

PF0

K13

PF1

L12

PF2

K12

PF3

J12

PF4

K11

PF5/SCIDETECT

C10

PF6

A9

PF7

W4

PG0/nCFOE

AA1

PG1/nCFWE

AA2

PG2/nCFIORD

AB1

PG3/nCFIOWR

AB2

PG4/nCFREG

AA3

PG5/nCFCE1

AB3

PG6/nCFCE2

Y3

PG7/PCDIR

AB4

PH0/CFRESETA

PH1/CFA8/CFA24/

CFRESETB

Y4

PH2/nCFENA

AB5

PH3/CFA9/CFA25/nCFENB GPIO Port H/Compact Flash Address Bit 9/PCMCIA1 Address Bit 25/PCMCIA2 Enable B

AA5

PH4/nCFWAIT/nCFWAITA

GPIO Port H/Compact Flash WAIT Signal/PCMCIA WAIT A

W5

PH5/CFA10/nCFWAITB

GPIO Port H/Compact Flash Address Bit 10/PCMCIA2 WAIT B

AB6

PH6/AC97RESET

GPIO Port H/AC97 reset

Y6

PH7/nCFSTATEN

GPIO Port H/Compact Flash Status Read Enable

U3

LCDFP/LCDSPS

LCD Frame Pulse / HR-TFT Reset Row Driver Counter

V1

LCDLP/LCDHRLP

LCD Linepulse / HR-TFT Latch Pulse

U4

LCDCLS

HR-TFT Clock for Row Drivers

V2

LCDSPL

HR-TFT Start Pulse Left for reverse scanning

V3

LCDUBL

HR-TFT Up, Down signal for reverse scanning

V4

LCDSPR

HR-TFT Start Pulse Right for normal scanning

W1

LCDLBR

HR-TFT Output for reverse scanning

PD2/LCDVD10

PD3/LCDVD11

GPIO Port E and LCD Video Data Interface

16 mA

GPIO Port E

16 mA

GPIO Port F and Smart Card Interface. Can be used for external interrupts.

Interrupts can be level or edge triggered and are internally debounced.

8 mA

GPIO Port G/Compact Flash Output Enable

GPIO Port G/Compact Flash Write Enable

GPIO Port G/Compact Flash I/O read strobe

GPIO Port G/Compact Flash I/O write strobe

GPIO Port G/Compact Flash Register memory access

GPIO Port G/Compact Flash Chip Enable 1

GPIO Port G/Compact Flash Chip Enable 2

GPIO Port G/PC Card Direction

GPIO Port H/Compact Flash Reset A

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

AA4

GPIO Port H/Compact Flash Address Bit 8/PCMCIA1 Address Bit 24/PCMCIA2 Reset B

8 mA

GPIO Port H/Compact Flash Enable A

8 mA

8 mA

8 mA

8 mA

8 mA

8 mA

16 mA

16 mA

16 mA

16 mA

16 mA

16 mA

16 mA

Table 1. Functional Pin List (Cont’d)

BGA

SIGNAL

DESCRIPTION

OUTPUT

DRIVE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| SHD501290 | HERMETIC ULTRA LOW DROPOUT LINEAR REGULATOR |

| SHD526030 | POSITIVE ADJUSTABLE 1.5 AMP REGULATOR |

| SHD526150 | LINEAR VOLTAGE REGULATOR THREE TERMINAL-POSITIVE-ADJUSTABLE 3.0 Amp, Low Dropout Voltage TO-257 Hermetic Package |

| SHD674122 | HERMETIC SILICON CARBIDE RECTIFIER |

| SHD674122B | HERMETIC SILICON CARBIDE RECTIFIER |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| SHAUN | 制造商:Nwazet 功能描述:Raspberry Pi "Shaun" Case |

| SH-AX1000-CQ352RTFG896-A | 制造商:Microsemi Corporation 功能描述:SH-AX1000-CQ352RTFG896-A - Bulk |

| SH-AX2000-CQ352RTFG896-A | 制造商:Microsemi Corporation 功能描述:SH-AX2000-CQ352RTFG896-A - Bulk |

| SH-AX250-CQ352RTFG484S-A | 制造商:Microsemi Corporation 功能描述:SH-AX250-CQ352RTFG484S-A - Bulk |

| SHB | 制造商:PREMO 制造商全稱:PREMO CORPORATION S.L 功能描述:SMD Power Inductors Shielded |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。