- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄22024 > EPF8452ATC100-4 (Altera)IC FLEX 8000A FPGA 4K 100-TQFP PDF資料下載

參數(shù)資料

| 型號: | EPF8452ATC100-4 |

| 廠商: | Altera |

| 文件頁數(shù): | 37/62頁 |

| 文件大小: | 0K |

| 描述: | IC FLEX 8000A FPGA 4K 100-TQFP |

| 產(chǎn)品培訓(xùn)模塊: | Three Reasons to Use FPGA's in Industrial Designs |

| 標(biāo)準(zhǔn)包裝: | 270 |

| 系列: | FLEX 8000 |

| LAB/CLB數(shù): | 42 |

| 邏輯元件/單元數(shù): | 336 |

| 輸入/輸出數(shù): | 68 |

| 門數(shù): | 4000 |

| 電源電壓: | 4.75 V ~ 5.25 V |

| 安裝類型: | 表面貼裝 |

| 工作溫度: | 0°C ~ 85°C |

| 封裝/外殼: | 100-TQFP |

| 供應(yīng)商設(shè)備封裝: | 100-TQFP(14x14) |

| 產(chǎn)品目錄頁面: | 602 (CN2011-ZH PDF) |

| 其它名稱: | 544-2260 |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁當(dāng)前第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁

42

Altera Corporation

FLEX 8000 Programmable Logic Device Family Data Sheet

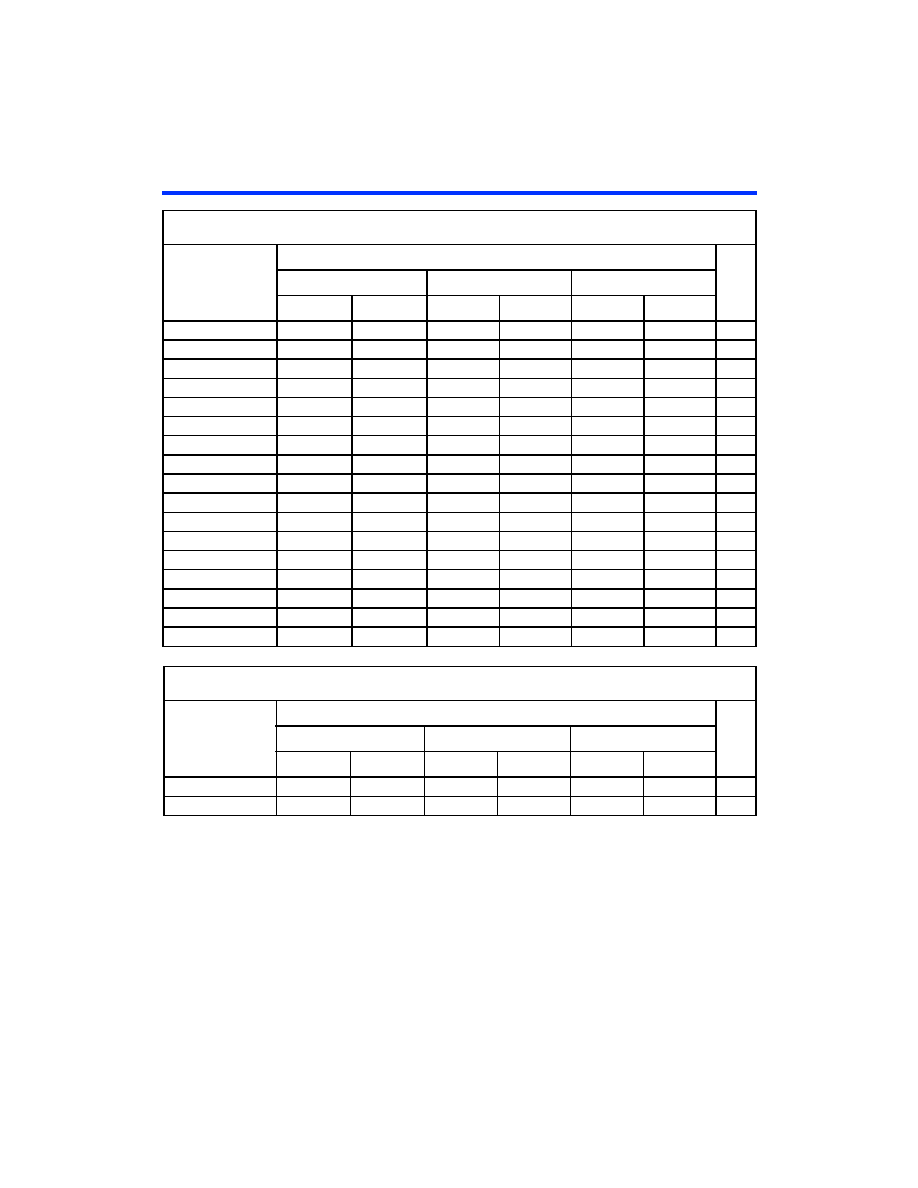

Table 32. EPF8452A LE Timing Parameters

Symbol

Speed Grade

Unit

A-2

A-3

A-4

Min

Max

Min

Max

Min

Max

t LUT

2.0

2.3

3.0

ns

t CLUT

0.0

0.2

0.1

ns

t RLUT

0.9

1.6

ns

t GATE

0.0

ns

t CASC

0.6

0.7

0.9

ns

t CICO

0.4

0.5

0.6

ns

t CGEN

0.4

0.9

0.8

ns

t CGENR

0.9

1.4

1.5

ns

t C

1.6

1.8

2.4

ns

t CH

4.0

ns

t CL

4.0

ns

t CO

0.4

0.5

0.6

ns

t COMB

0.4

0.5

0.6

ns

t SU

0.8

1.0

1.1

ns

t H

0.9

1.1

1.4

ns

t PRE

0.6

0.7

0.8

ns

t CLR

0.6

0.7

0.8

ns

Table 33. EPF8452A External Timing Parameters

Symbol

Speed Grade

Unit

A-2

A-3

A-4

Min

Max

Min

Max

Min

Max

tDRR

16.0

20.0

25.0

ns

tODH

1.0

ns

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MRA4007T3G | DIODE STD REC 1A 1000V SMA |

| ADT7461ARMZ-2REEL7 | IC SENSOR TEMP DGTL 2CH 8MSOP |

| RSC05DRAN | CONN EDGECARD 10POS R/A .100 SLD |

| EP4CE15E22C7N | IC CYCLONE IV E FPGA 15K 144EQFP |

| BAS70LT1G | DIODE SCHOTTKY 70V SOT23 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| EPF8452ATC100-4N | 功能描述:FPGA - 現(xiàn)場可編程門陣列 FPGA - Flex 8000 42 LABs 68 IOs RoHS:否 制造商:Altera Corporation 系列:Cyclone V E 柵極數(shù)量: 邏輯塊數(shù)量:943 內(nèi)嵌式塊RAM - EBR:1956 kbit 輸入/輸出端數(shù)量:128 最大工作頻率:800 MHz 工作電源電壓:1.1 V 最大工作溫度:+ 70 C 安裝風(fēng)格:SMD/SMT 封裝 / 箱體:FBGA-256 |

| EPF8452ATI100-3 | 制造商:未知廠家 制造商全稱:未知廠家 功能描述:Field Programmable Gate Array (FPGA) |

| EPF8452GC160-2 | 制造商:ALTEA 功能描述:Field-Programmable Gate Array, 336 Cell, 160 Pin, Ceramic, QFP 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 336 Cell, 160 Pin, Ceramic, QFP |

| EPF8452GC160-3 | 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 336 Cell, 160 Pin, Ceramic, PGA |

| EPF8452LC84-2 | 制造商:Altera Corporation 功能描述:Field-Programmable Gate Array, 336 Cell, 84 Pin, Plastic, PLCC |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。