- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄384759 > MT9041B (Mitel Networks Corporation) T1/E1 System Synchronizer PDF資料下載

參數(shù)資料

| 型號(hào): | MT9041B |

| 廠商: | Mitel Networks Corporation |

| 英文描述: | T1/E1 System Synchronizer |

| 中文描述: | T1/E1的系統(tǒng)同步 |

| 文件頁(yè)數(shù): | 4/19頁(yè) |

| 文件大?。?/td> | 72K |

| 代理商: | MT9041B |

第1頁(yè)第2頁(yè)第3頁(yè)當(dāng)前第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)

MT9041B

Advance Information

4

is well within the maximum phase slope of 7.6ns per

125us or 81ns per 1.326ms specified by Bellcore

GR-1244-CORE Stratum 4E.

Loop Filter

- the Loop Filter is similar to a first order

low pass filter with a 1.9 Hz cutoff frequency for all

three

reference

frequency

1.544MHz or 2.048MHz). This filter ensures that the

jitter transfer requirements in ETS 300 011 and AT&T

TR62411 are met.

selections

(8kHz,

Control Circuit

- the Control Circuit sets the mode

of the DPLL. The two possible modes are Normal

and Freerun.

Digitally Controlled Oscillator (DCO)

- the DCO

receives the limited and filtered signal from the Loop

FIlter, and based on its value, generates a

corresponding

digital

synchronization method of the DCO is dependent on

the state of the MT9041B.

output

signal.

The

In Normal Mode, the DCO provides an output signal

which is frequency and phase locked to the selected

input reference signal.

In Freerun Mode, the DCO is free running with an

accuracy equal to the accuracy of the OSCi 20MHz

source.

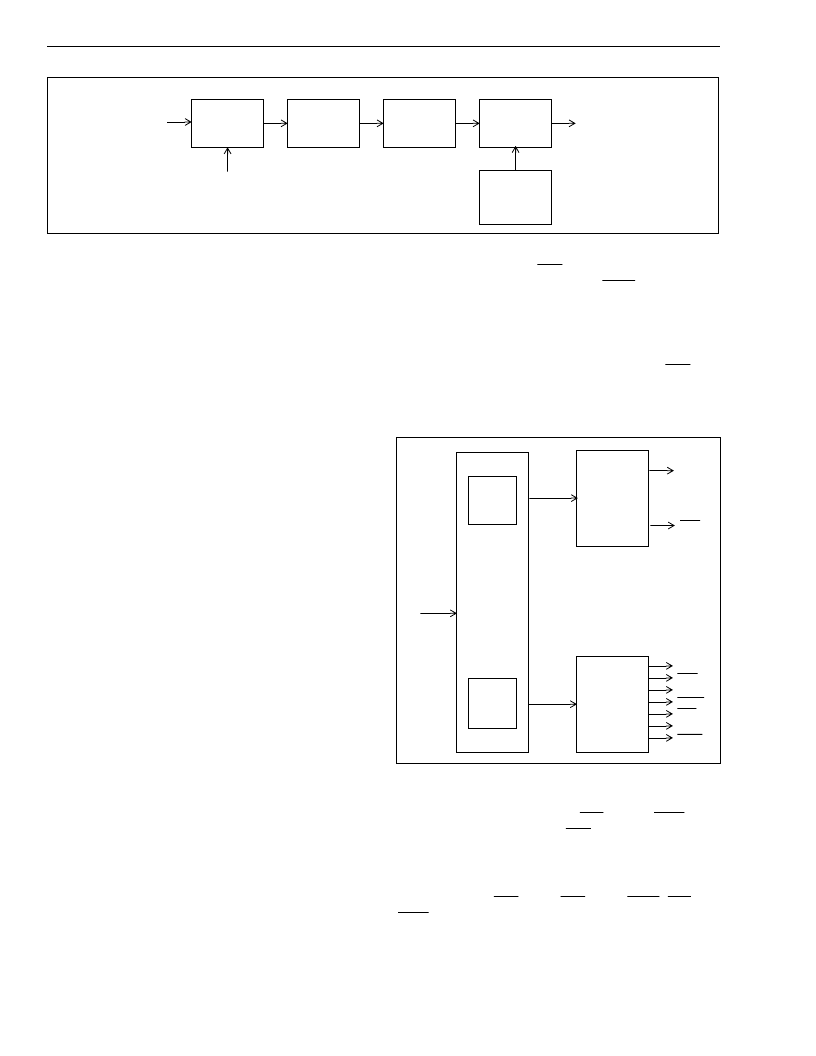

Output Interface Circuit

The output of the DCO (DPLL) is used by the Output

Interface Circuit to provide the output signals shown

in Figure 4. The Output Interface Circuit uses two

Tapped Delay Lines followed by a T1 Divider Circuit

and an E1 Divider Circuit to generate the required

output signals.

Two tapped delay lines are used to generate a

16.384MHz and a 12.352MHz signals.

The E1 Divider Circuit uses the 16.384MHz signal to

generate four clock outputs and three frame pulse

outputs. The C8o,

generated by simply dividing the C16o clock by two,

four and eight respectively. These outputs have a

nominal 50% duty cycle.

C4o and C2o clocks are

The T1 Divider Circuit uses the 12.384MHz signal to

generate two clock outputs. C1.5o and C3o are

generated by dividing the internal C12 clock by four

and eight respectively. These outputs have a nominal

50% duty cycle.

Figure 4 - Output Interface Circuit Block

Diagram

The frame pulse outputs (F0o, F8o, F16o) are

generated directly from the C16 clock.

The T1 and E1 signals are generated from a

common DPLL signal. Consequently, the clock

outputs C1.5o, C3o, C2o, C4o, C8o, C16o, F0o and

F16o are locked to one another for all operating

states, and are also locked to the selected input

reference in Normal Mode. See Figures 11 and 12.

Tapped

Delay

Line

From

DPLL

T1 Divider

E1 Divider

16MHz

12MHz

C3o

C1.5o

C2o

C4o

C8o

C16o

F0o

F8o

F16o

Tapped

Delay

Line

Figure 3 - DPLL Block Diagram

Control

Circuit

Feedback Signal

from

Frequency Select MUX

DPLL Reference

to

Output Interface Circuit

REF Reference

Limiter

Loop Filter

Digitally

Controlled

Oscillator

Phase

Detector

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT9041BP | T1/E1 System Synchronizer |

| MT9041 | Multiple Output Trunk PLL |

| MT9041AP | IC REG LDO 150MA 5.0V 0.5% 8SOIC |

| MT9042C | Multitrunk System Synchronizer |

| MT9042CP | Multitrunk System Synchronizer |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT9041BP | 制造商:Microsemi Corporation 功能描述: 制造商:Zarlink Semiconductor Inc 功能描述:PCM, OTHER/SPECIAL/MISCELLANEOUS, 28 Pin, Plastic, PLCC |

| MT9041BP1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 5V 28PLCC - Rail/Tube 制造商:Microsemi Corporation 功能描述:PB FREE MULTIPLE OUTPUT TRUNK PLL 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1 /T1 5V 28PLCC - Rail/Tube 制造商:Zarlink Semiconductor Inc 功能描述:PB FREE MULTIPLE OUTPUT TRUNK PLL |

| MT9041BPR | 制造商:Microsemi Corporation 功能描述:SPECIALTY TELECOM CIRCUIT, 28 Pin Plastic PLCC |

| MT9041BPR1 | 制造商:Microsemi Corporation 功能描述:FRAMER E1 /T1 5V 28PLCC - Tape and Reel 制造商:Zarlink Semiconductor Inc 功能描述:FRAMER E1 /T1 5V 28PLCC - Tape and Reel |

| MT9042 | 制造商:MITEL 制造商全稱:Mitel Networks Corporation 功能描述:Global Digital Trunk Synchronizer |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。