- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄98045 > MT8LLN22NCNE PCI BUS CONTROLLER, PBGA316 PDF資料下載

參數(shù)資料

| 型號: | MT8LLN22NCNE |

| 元件分類: | 總線控制器 |

| 英文描述: | PCI BUS CONTROLLER, PBGA316 |

| 封裝: | 27 X 27 MM, PLASTIC, BGA-316 |

| 文件頁數(shù): | 11/145頁 |

| 文件大小: | 2285K |

| 代理商: | MT8LLN22NCNE |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁當(dāng)前第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁第62頁第63頁第64頁第65頁第66頁第67頁第68頁第69頁第70頁第71頁第72頁第73頁第74頁第75頁第76頁第77頁第78頁第79頁第80頁第81頁第82頁第83頁第84頁第85頁第86頁第87頁第88頁第89頁第90頁第91頁第92頁第93頁第94頁第95頁第96頁第97頁第98頁第99頁第100頁第101頁第102頁第103頁第104頁第105頁第106頁第107頁第108頁第109頁第110頁第111頁第112頁第113頁第114頁第115頁第116頁第117頁第118頁第119頁第120頁第121頁第122頁第123頁第124頁第125頁第126頁第127頁第128頁第129頁第130頁第131頁第132頁第133頁第134頁第135頁第136頁第137頁第138頁第139頁第140頁第141頁第142頁第143頁第144頁第145頁

Coppertail Product Specification

MT8LLN22NCNE.fm – Rev. 1, Pub. 2/02

108

2002, Micron Technology Inc.

PRELIMINARY

MT8LLN22NCNE

COPPERTAIL

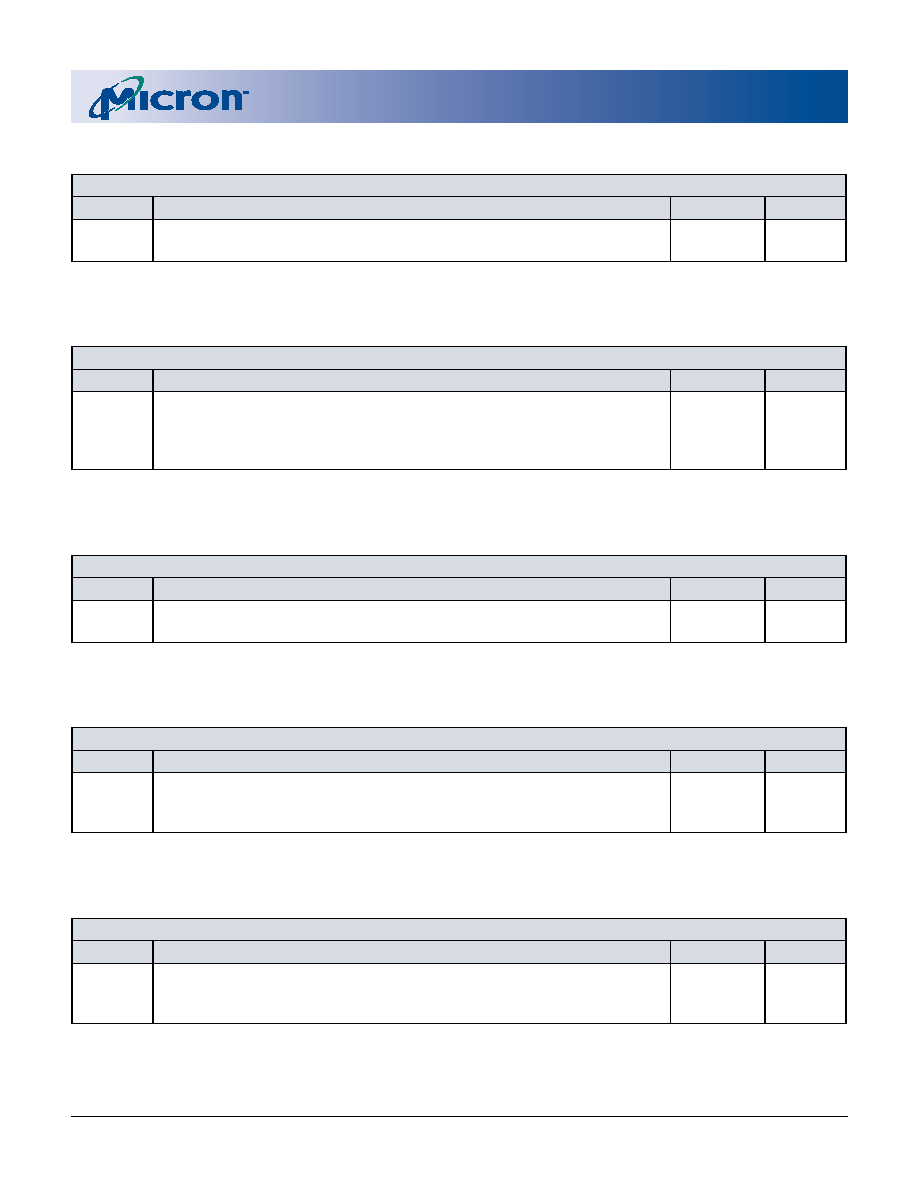

Standby General Purpose I/O Status

NOTE:

Register is standby powered and unaffected by SB_POWEROK or P_RST#. Reset only with RSMRST#.

Standby General Purpose I/O Event Enable

NOTE:

Register is standby powered and unaffected by SB_POWEROK or P_RST#. Reset only with RSMRST#.

Standby General Purpose I/O Input Value

NOTE:

Register is standby powered and unaffected by SB_POWEROK or P_RST#. Reset only with RSMRST#.

Standby General Purpose I/O Input Polarity Sense

NOTE:

Register is standby powered and unaffected by SB_POWEROK or P_RST#. Reset only with RSMRST#.

Standby General Purpose I/O Output Value

NOTE:

Register is standby powered and unaffected by SB_POWEROK or P_RST#. Reset only with RSMRST#.

ADDRESS: ACPI_BASE + 80h

SYMBOL: SGPIO_STS

BITS

DESCRIPTION

PROPERTIES

RESET

15:0

GPIO_VAUX[15:0] Status. When a bit corresponding to a GPIO_VAUX is

set, the GPIO_VAUX event has occurred.

R/WOTC

0

ADDRESS: ACPI_BASE + 82h

SYMBOL: SGPIO_EVT_EN

BITS

DESCRIPTION

PROPERTIES

RESET

15:0

GPIO_VAUX[15:0] Event Enable. When a bit corresponding to a

GPIO_VAUX is set, the GPIO_VAUX event is enabled and will set GPSTS0

bit 8. When a bit corresponding to a GPIO_VAUX is clear, the GPIO_VAUX

event is disabled.

R/W

0

ADDRESS: ACPI_BASE + 84h

SYMBOL: SGPIO_IN_VAL

BITS

DESCRIPTION

PROPERTIES

RESET

15:0

GPIO_VAUX[15:0] Input value. Each bit represents the input value of a

corresponding GPIO_VAUX.

R/O

0

ADDRESS: ACPI_BASE + 86h

SYMBOL: SGPIO_POLSNS

BITS

DESCRIPTION

PROPERTIES

RESET

15:0

GPIO_VAUX[15:0] Sense. When a bit corresponding to a GPIO_VAUX is

set, the GPIO_VAUX event sense is active high. When a bit corresponding

to a GPIO_VAUX is clear, the GPIO_VAUX event sense is active low.

R/W

0

ADDRESS: ACPI_BASE + 88h

SYMBOL: SGPIO_OUT_VAL

BITS

DESCRIPTION

PROPERTIES

RESET

15:0

GPIO_VAUX[15:0] Output Value. Each bit represents the output value of

a corresponding GPIO_VAUX. This value will appear on the GPIO_VAUX

output pin when enabled.

R/W

0

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MTB10N40ET4 | 10 A, 400 V, 0.55 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB15N06V | 15 A, 60 V, 0.12 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB15N06VT4 | 15 A, 60 V, 0.12 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB16N25E | 16 A, 250 V, 0.25 ohm, N-CHANNEL, Si, POWER, MOSFET |

| MTB16N25ET4 | 16 A, 250 V, 0.25 ohm, N-CHANNEL, Si, POWER, MOSFET |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT8LLN22NCNE-A | 制造商:Micron Technology Inc 功能描述:COPPERTAIL CHIPSET - Trays |

| MT8LLN22NCNE-A2 | 制造商:Micron Technology Inc 功能描述:COPPERTAIL CHIPSET AND MOTHERBOARD - Trays |

| MT8LSDF3264WG-133D1 | 制造商:Micron Technology Inc 功能描述:256MB 32MX64 SYNCH DRAM MODULE MICRO DIMM 3.3V - Trays |

| MT8LSDT1664 | 制造商:Micron Technology Inc 功能描述:128MB 16MX64 SDRAM MODULE PBF DIMM 3.3V - Trays |

| MT8LSDT1664AG-10EB1 | 制造商:Micron Technology Inc 功能描述:DRAM MOD SDRAM 1GBIT 168UDIMM - Trays |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。