- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄296642 > MT48H8M16LFB4-8IT:JTR 8M X 16 SYNCHRONOUS DRAM, 6 ns, PBGA54 PDF資料下載

參數(shù)資料

| 型號(hào): | MT48H8M16LFB4-8IT:JTR |

| 元件分類: | DRAM |

| 英文描述: | 8M X 16 SYNCHRONOUS DRAM, 6 ns, PBGA54 |

| 封裝: | 8 X 8 MM, LEAD FREE, VFBGA-54 |

| 文件頁數(shù): | 20/61頁 |

| 文件大?。?/td> | 2469K |

第1頁第2頁第3頁第4頁第5頁第6頁第7頁第8頁第9頁第10頁第11頁第12頁第13頁第14頁第15頁第16頁第17頁第18頁第19頁當(dāng)前第20頁第21頁第22頁第23頁第24頁第25頁第26頁第27頁第28頁第29頁第30頁第31頁第32頁第33頁第34頁第35頁第36頁第37頁第38頁第39頁第40頁第41頁第42頁第43頁第44頁第45頁第46頁第47頁第48頁第49頁第50頁第51頁第52頁第53頁第54頁第55頁第56頁第57頁第58頁第59頁第60頁第61頁

PDF: 09005aef8237e877/Source: 09005aef8237e8d8

Micron Technology, Inc., reserves the right to change products or specifications without notice.

128Mb_x16 Mobile SDRAM_Y25M_2.fm - Rev. A 6/06 EN

27

2006 Micron Technology, Inc. All rights reserved.

128Mb: x16 Mobile SDRAM

READs

Preliminary

In the case of a fixed-length burst being executed to completion, a PRECHARGE

command issued at the optimum time (as described above) provides the same operation

that would result from the same fixed-length burst with auto precharge. The disadvan-

tage of the PRECHARGE command is that it requires that the command and address

buses be available at the appropriate time to issue the command; the advantage of the

PRECHARGE command is that it can be used to truncate fixed-length bursts.

Fixed-length WRITE bursts can be truncated with the BURST TERMINATE command.

When truncating a WRITE burst, the input data applied coincident with the BURST

TERMINATE command will be ignored. The last data written (provided that DQM is

LOW at that time) will be the input data applied one clock previous to the BURST

TERMINATE command. This is shown in Figure 23 on page 29, where data n is the last

desired data element of a longer burst.

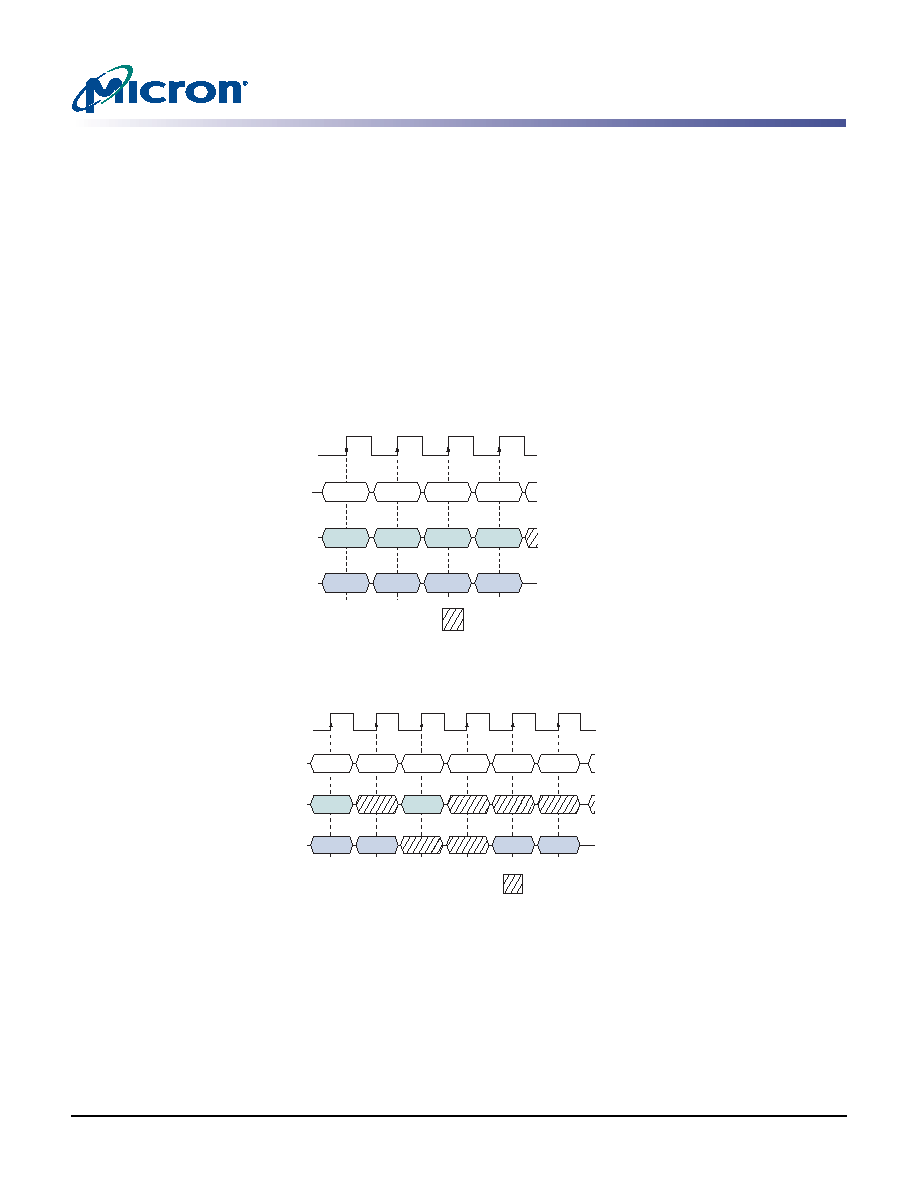

Figure 19:

Random WRITE Cycles

Notes:

1. Each WRITE command may be to any bank. DQM is LOW.

Figure 20:

WRITE-To-READ

Notes:

1. The WRITE command may be to any bank, and the READ command may be to any bank.

DQM is LOW.

CLK

DQ

DIN

n

T2

T1

T0

COMMAND

ADDRESS

WRITE

BANK,

COL n

DIN

a

DIN

x

DIN

m

WRITE

BANK,

COL a

BANK,

COL x

BANK,

COL m

DON’T CARE

T3

CLK

DQ

COMMAND

ADDRESS

NOP

WRITE

BANK,

COL n

DIN

n

DIN

n + 1

DOUT

b

READ

NOP

BANK,

COL b

NOP

DOUT

b + 1

DON’T CARE

CL = 2

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| MT48LC4M32TG-10 | 4M X 32 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| MT48V8M16LFB4-8XT | 8M X 16 SYNCHRONOUS DRAM, 7 ns, PBGA54 |

| MT48LC4M32LFB5-10ES:G | 4M X 32 SYNCHRONOUS DRAM, 7 ns, PBGA90 |

| MT48V4M32TG-8XT | 4M X 32 SYNCHRONOUS DRAM, 7 ns, PDSO54 |

| MT48LC8M8A2TG-8EL:GIT | 8M X 8 SYNCHRONOUS DRAM, 6 ns, PDSO54 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| MT48H8M16LFF3-7E | 制造商:Micron Technology Inc 功能描述: |

| MT48H8M16LFF4-10 | 功能描述:IC SDRAM 128MBIT 100MHZ 54VFBGA RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SDRAM 存儲(chǔ)容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

| MT48H8M16LFF4-10 IT | 功能描述:IC SDRAM 128MBIT 100MHZ 54VFBGA RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SDRAM 存儲(chǔ)容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

| MT48H8M16LFF4-8 | 功能描述:IC SDRAM 128MBIT 125MHZ 54VFBGA RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SDRAM 存儲(chǔ)容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

| MT48H8M16LFF4-8 IT | 功能描述:IC SDRAM 128MBIT 125MHZ 54VFBGA RoHS:否 類別:集成電路 (IC) >> 存儲(chǔ)器 系列:- 標(biāo)準(zhǔn)包裝:1 系列:- 格式 - 存儲(chǔ)器:RAM 存儲(chǔ)器類型:SDRAM 存儲(chǔ)容量:256M(8Mx32) 速度:143MHz 接口:并聯(lián) 電源電壓:3 V ~ 3.6 V 工作溫度:-40°C ~ 85°C 封裝/外殼:90-VFBGA 供應(yīng)商設(shè)備封裝:90-VFBGA(8x13) 包裝:托盤 其它名稱:Q2841869 |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。