- 您現(xiàn)在的位置:買賣IC網(wǎng) > PDF目錄359067 > M48TMH1 (意法半導體) 5V PC REAL TIME CLOCK PDF資料下載

參數(shù)資料

| 型號: | M48TMH1 |

| 廠商: | 意法半導體 |

| 英文描述: | 5V PC REAL TIME CLOCK |

| 中文描述: | 5V的電腦實時時鐘 |

| 文件頁數(shù): | 13/23頁 |

| 文件大小: | 163K |

| 代理商: | M48TMH1 |

13/23

M48T86

read valid time and date information. If this inter-

rupt is used, the IRQF bit (Register C; Bit 7) should

be cleared before leaving the interrupt routine.

A second method uses the Update-In-Progress

(UIP) bit (Register A; Bit 7) to determine if the up-

date cycle is in progress. The UIP bit will pulse

once per second. After the UIP bit goes high, the

update transfer occurs 244μs later. If a low is read

on the UIP bit, the user has at least 244μs before

the time/calendar data will be changed. Therefore,

the user should avoid interrupt service routines

that would cause the time needed to read valid

time/calendar data to exceed 244μs.

The third method uses a periodic interrupt to deter-

mine if an update cycle is in progress. The UIP bit

is set high between the setting of the PF bit (Reg-

ister C; Bit 6). Periodic interrupts that occur at a

rate greater than t

BUC

allow valid time and date in-

formation to be reached at each occurrence of the

periodic interrupt.The reads should be completed

within 1/(t

PL/2

+ t

BUC

) to ensure that data is not

read during the update cycle.

UPDATE CYCLE

The M48T86 executes an update cycle once per

second regardless of the SET bit (Register B; Bit

7). When the SET bit is asserted, the user copy of

the double buffered time, calendar, and alarm

bytes is frozen and will not update as the time in-

crements. However, the time countdown chain

continues to update the internal copy of the buffer.

This feature allows accurate time to be main-

tained, independent of reading and writing the

time, calendar, and alarm buffers. This also guar-

antees that the time and calendar information will

be consistent. The update cycle also compares

each alarm byte with the corresponding time byte

and issues an alarm if a match or if a "don't care"

code is present in all three positions.

There are three methods of accessing the real

time clock that will avoid any possibility of obtain-

ing inconsistent time and calendar data. The first

method uses the update-ended interrupt. If en-

abled, an interrupt occurs after every update cycle

which indicates that over 999ms are available to

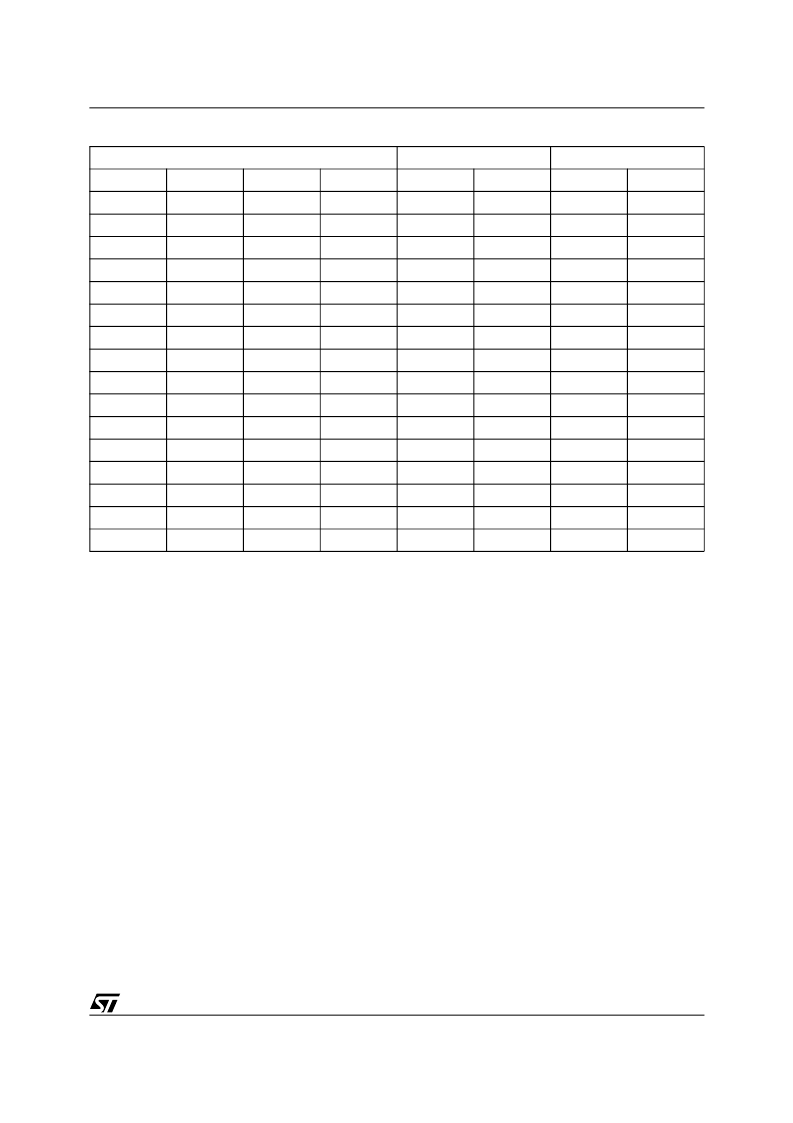

Table 10. Square Wave Frequency/Periodic Interrupt Rate

Register A Bits

Square Wave

Periodic Interrupt

RS3

RS2

RS1

RS0

Frequency

Units

Period

Units

0

0

0

0

None

None

0

0

0

1

256

Hz

3.90625

ms

0

0

1

0

128

Hz

7.8125

ms

0

0

1

1

8.192

kHz

122.070

us

0

1

0

0

4.096

kHz

244.141

us

0

1

0

1

2.048

kHz

488.281

us

0

1

1

0

1.024

kHz

976.5625

us

0

1

1

1

512

Hz

1.953125

ms

1

0

0

0

256

Hz

3.90625

ms

1

0

0

1

128

Hz

7.8125

ms

1

0

1

0

64

Hz

15.625

ms

1

0

1

1

32

Hz

31.25

ms

1

1

0

0

16

Hz

62.5

ms

1

1

0

1

8

Hz

125

ms

1

1

1

0

4

Hz

250

ms

1

1

1

1

2

Hz

500

ms

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| M48TMH1TR | 5V PC REAL TIME CLOCK |

| M48TY-85MH1 | 3.3V-5V TIMEKEEPER CONTROLLER |

| M48TY-85MH1TR | 3.3V-5V TIMEKEEPER CONTROLLER |

| M48TY-85PM1 | 3.3V-5V 1 Mbit 128Kb x8 TIMEKEEPER SRAM |

| M48Z02 | 16 Kbit 2Kb x 8 ZEROPOWER SRAM |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| M48TMH1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V PC REAL TIME CLOCK |

| M48TPC1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V PC REAL TIME CLOCK |

| M48TPC1TR | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:5V PC REAL TIME CLOCK |

| M4-8TP-RJ45 | 制造商:Hirschmann Electronics GmbH & Co Kg 功能描述:Media Module, MACH 4000, 8xRJ45 (10/100 Meg) + 8xRJ45 (10 Meg) Copper Ports |

| M48TV-70MH1 | 制造商:STMICROELECTRONICS 制造商全稱:STMicroelectronics 功能描述:3.3V-5V TIMEKEEPER CONTROLLER |

發(fā)布緊急采購,3分鐘左右您將得到回復(fù)。