- 您現在的位置:買賣IC網 > PDF目錄66943 > 94063-807LF 7 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER PDF資料下載

參數資料

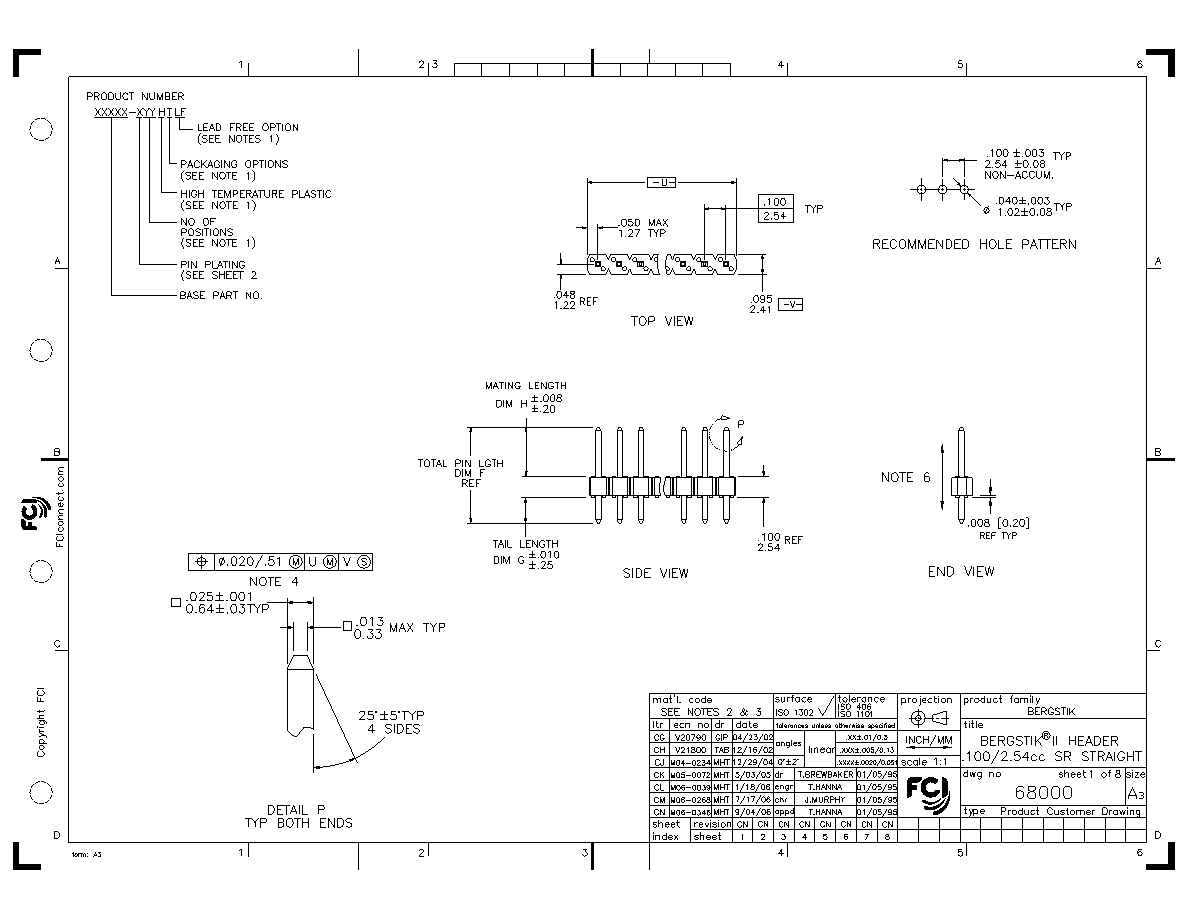

| 型號: | 94063-807LF |

| 元件分類: | 電路板相疊連接器 |

| 英文描述: | 7 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| 封裝: | LEAD FREE |

| 文件頁數: | 1/8頁 |

| 文件大小: | 693K |

| 代理商: | 94063-807LF |

PDM: Rev:CN

Released

.

STATUS:

Printed: Sep 09, 2006

相關PDF資料 |

PDF描述 |

|---|---|

| 94063-812LF | 12 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| 94063-813LF | 13 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| 94063-923LF | 23 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| 94063-928LF | 28 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

| 94094-017LF | 17 CONTACT(S), MALE, STRAIGHT TWO PART BOARD CONNECTOR, SOLDER |

相關代理商/技術參數 |

參數描述 |

|---|---|

| 940639-000 | 制造商:TE Connectivity 功能描述:CBL 3CNDCTR 16AWG TNNED CPPR 600V - Cable Rools/Shrink Tubing 制造商:TE Connectivity 功能描述:55PC0231-16-3/6/9 |

| 9406-4 | 制造商:API Delevan 功能描述:IND RF SHLD 286NH 25MHZ 52 FERRITE RDL - Bulk |

| 940-640 | 功能描述:支架與墊片 Plastic Spcr .64 in Nylon White RoHS:否 制造商:Schurter 類型:Transipillar Spacers 長度:16 m 螺紋大小:M4 外徑:10 mm 材料:Nylon with Steel 電鍍:Zinc |

| 9406-40 | 功能描述:固定電感器 220uH 0% 9.7ohm HznMnt TuneVari Coil RoHS:否 制造商:AVX 電感:10 uH 容差:20 % 最大直流電流:1 A 最大直流電阻:0.075 Ohms 工作溫度范圍:- 40 C to + 85 C 自諧振頻率:38 MHz Q 最小值:40 尺寸:4.45 mm W x 6.6 mm L x 2.92 mm H 屏蔽:Shielded 端接類型:SMD/SMT 封裝 / 箱體:6.6 mm x 4.45 mm |

| 9406-40 250 BULK | 制造商:API Delevan 功能描述:INDUCTOR MOUNTED TUNABLE VARIABL |

發(fā)布緊急采購,3分鐘左右您將得到回復。