- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄223392 > ASMT-MWB1-NGGL1 SINGLE COLOR LED, COOL WHITE, 5.26 mm PDF資料下載

參數(shù)資料

| 型號(hào): | ASMT-MWB1-NGGL1 |

| 元件分類: | LED |

| 英文描述: | SINGLE COLOR LED, COOL WHITE, 5.26 mm |

| 封裝: | ROHS COMPLIANT PACKAGE-2 |

| 文件頁(yè)數(shù): | 11/13頁(yè) |

| 文件大?。?/td> | 211K |

| 代理商: | ASMT-MWB1-NGGL1 |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)當(dāng)前第11頁(yè)第12頁(yè)第13頁(yè)

7

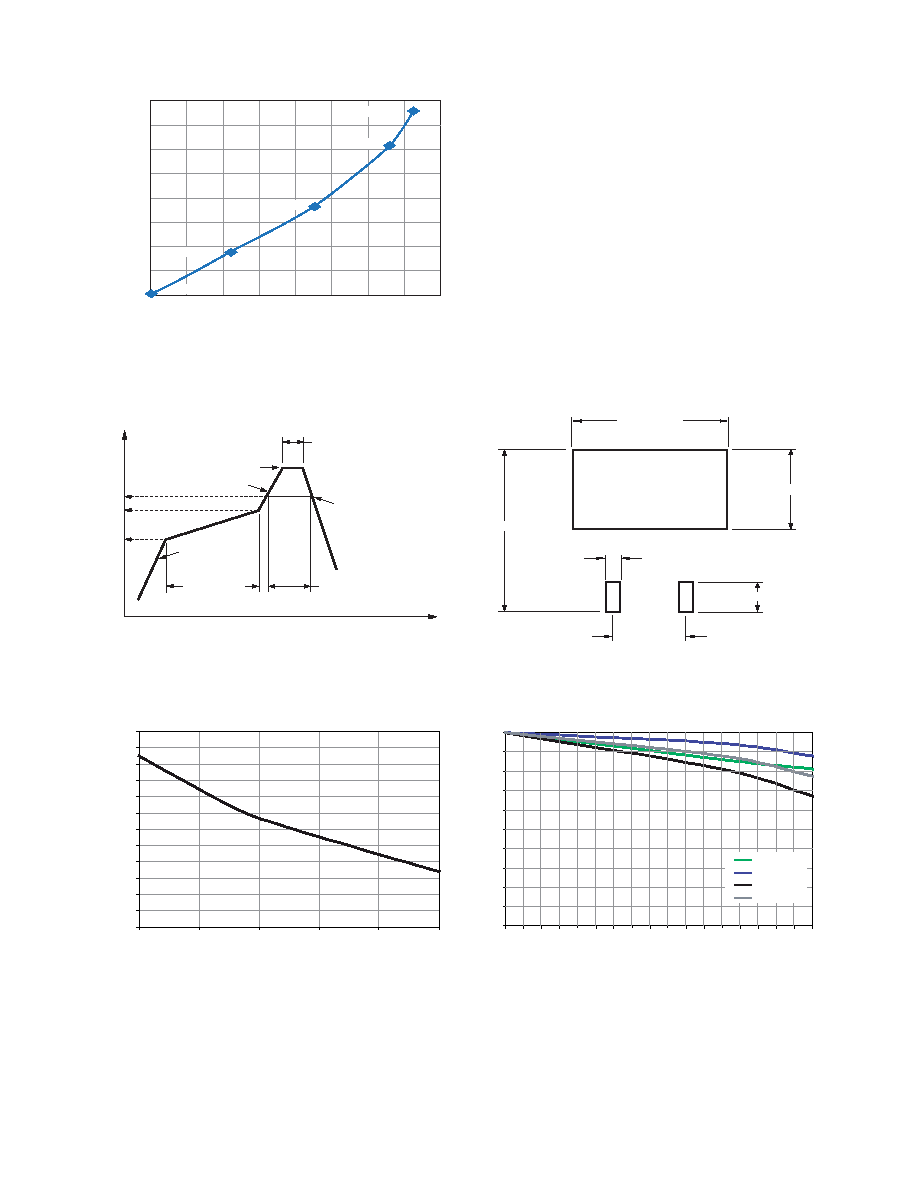

Figure 13. Chromaticity shift vs. current

*Note: (x,y) values @ 350 mA reference to (0.0)

Figure 14. Recommended reflow soldering profile

Figure 15. Recommended soldering land pattern

Figure 16. Temperature vs. relative forward voltage shift

Figure 17. Relative LOP vs Junction Temperature for InGaN Devices

Note:

For detail information on reflow soldering of Avago surface mount LEDs, do refer to Avago Application Note AN1060 Surface Mounting SMT LED

Indicator Components.

217 °C

200 °C

150 °C

60 - 120 SEC.

-6 °C/SEC. MAX.

3 °C/SEC. MAX.

255 - 260 °C

100 SEC. MAX.

10 - 30 SEC.

TIME

TE

MP

ERATURE

(Acc. to J-STD-020C)

17.00 ± 0.20

1.00 ± 0.10

3.1 ± 0.10

8.40 ± 0.10

5.08 ± 0.10

10.70 ± 0.10

Y-

COO

R

D

INATE

S

0

0.002

0

X-COORDINATES

0.008

0.014

0.003

0.002

0.001

0.016

0.004 0.005 0.006

0.01

0.007

0.008

0.006

0.004

0.012

100 mA

150 mA

250 mA

300 mA

350 mA

-300

-250

-200

-150

-100

-50

0

50

100

150

200

250

300

-40

-15

10

35

60

85

TEMPERATURE - °C

RELATIVE

F

O

RWAR

D

V

O

LTAGE

SHIFT

(m

V)

0

10

20

30

40

50

60

70

80

90

100

25 30 35 40 45 50 55 60 65 70 75 80 85 90 95 100105110

JUNCTION TEMPERATURE (°C)

RELATIVE

L

OP

(%)

GREEN

BLUE

COOL WHITE

WARM WHITE

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| ASMT-MWB1-NGKG1 | SINGLE COLOR LED, COOL WHITE, 5.26 mm |

| ASMT-MWB1-NEHR1 | SINGLE COLOR LED, COOL WHITE, 5.26 mm |

| ASMT-MWB1-NFH40 | SINGLE COLOR LED, COOL WHITE, 5.26 mm |

| ASMT-MWB1-NGHE0 | SINGLE COLOR LED, COOL WHITE, 5.26 mm |

| ASMT-MY00-NJJF0 | SINGLE COLOR LED, WARM WHITE, 5.26 mm |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| ASMT-MWB1-NGJ00 | 功能描述:大功率LED - 白色 Cool White, 1 Watt Moonstone RoHS:否 制造商:Cree, Inc. 照明顏色:Cool White 顏色溫度:5000 K 光通量:280 lm 顯示角:125 deg 正向電流:700 mA 正向電壓:2.9 V 安裝風(fēng)格:SMD/SMT 系列:XMLBWW 封裝:Reel |

| ASMT-MWB1-NJK00 | 功能描述:大功率LED - 白色 Cool White, 1 Watt Moonstone RoHS:否 制造商:Cree, Inc. 照明顏色:Cool White 顏色溫度:5000 K 光通量:280 lm 顯示角:125 deg 正向電流:700 mA 正向電壓:2.9 V 安裝風(fēng)格:SMD/SMT 系列:XMLBWW 封裝:Reel |

| ASMT-MWB2-NGH00 | 功能描述:大功率LED - 白色 Cool White, 1 Watt Moonstone RoHS:否 制造商:Cree, Inc. 照明顏色:Cool White 顏色溫度:5000 K 光通量:280 lm 顯示角:125 deg 正向電流:700 mA 正向電壓:2.9 V 安裝風(fēng)格:SMD/SMT 系列:XMLBWW 封裝:Reel |

| ASMT-MWB4-NKM00 | 功能描述:大功率LED - 白色 Cool White 1 Watt Moonstone RoHS:否 制造商:Cree, Inc. 照明顏色:Cool White 顏色溫度:5000 K 光通量:280 lm 顯示角:125 deg 正向電流:700 mA 正向電壓:2.9 V 安裝風(fēng)格:SMD/SMT 系列:XMLBWW 封裝:Reel |

| ASMT-MWB6-NLM00 | 功能描述:大功率LED - 白色 Cool White 1 Watt RoHS:否 制造商:Cree, Inc. 照明顏色:Cool White 顏色溫度:5000 K 光通量:280 lm 顯示角:125 deg 正向電流:700 mA 正向電壓:2.9 V 安裝風(fēng)格:SMD/SMT 系列:XMLBWW 封裝:Reel |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。