- 您現(xiàn)在的位置:買(mǎi)賣(mài)IC網(wǎng) > PDF目錄166515 > BU-61582D3-430Z (DATA DEVICE CORP) 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 PDF資料下載

參數(shù)資料

| 型號(hào): | BU-61582D3-430Z |

| 廠商: | DATA DEVICE CORP |

| 元件分類(lèi): | 微控制器/微處理器 |

| 英文描述: | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| 封裝: | CERAMIC, DIP-70 |

| 文件頁(yè)數(shù): | 25/48頁(yè) |

| 文件大小: | 378K |

| 代理商: | BU-61582D3-430Z |

第1頁(yè)第2頁(yè)第3頁(yè)第4頁(yè)第5頁(yè)第6頁(yè)第7頁(yè)第8頁(yè)第9頁(yè)第10頁(yè)第11頁(yè)第12頁(yè)第13頁(yè)第14頁(yè)第15頁(yè)第16頁(yè)第17頁(yè)第18頁(yè)第19頁(yè)第20頁(yè)第21頁(yè)第22頁(yè)第23頁(yè)第24頁(yè)當(dāng)前第25頁(yè)第26頁(yè)第27頁(yè)第28頁(yè)第29頁(yè)第30頁(yè)第31頁(yè)第32頁(yè)第33頁(yè)第34頁(yè)第35頁(yè)第36頁(yè)第37頁(yè)第38頁(yè)第39頁(yè)第40頁(yè)第41頁(yè)第42頁(yè)第43頁(yè)第44頁(yè)第45頁(yè)第46頁(yè)第47頁(yè)第48頁(yè)

31

Data Device Corporation

www.ddc-web.com

BU-61582

G-08/02-250

SELECT

MSB/LSB

MEM/REG

A15-A0

ADDRESS_LAT

SELECT

MSB/LSB

MEM/REG

A15-A0

(1)

(2)

(3)

(4)

(1)

(2)

(3)

(4)

(5)

t1

INTERNAL

VALUES

INPUT

SIGNALS

t2

t4

t5

t3

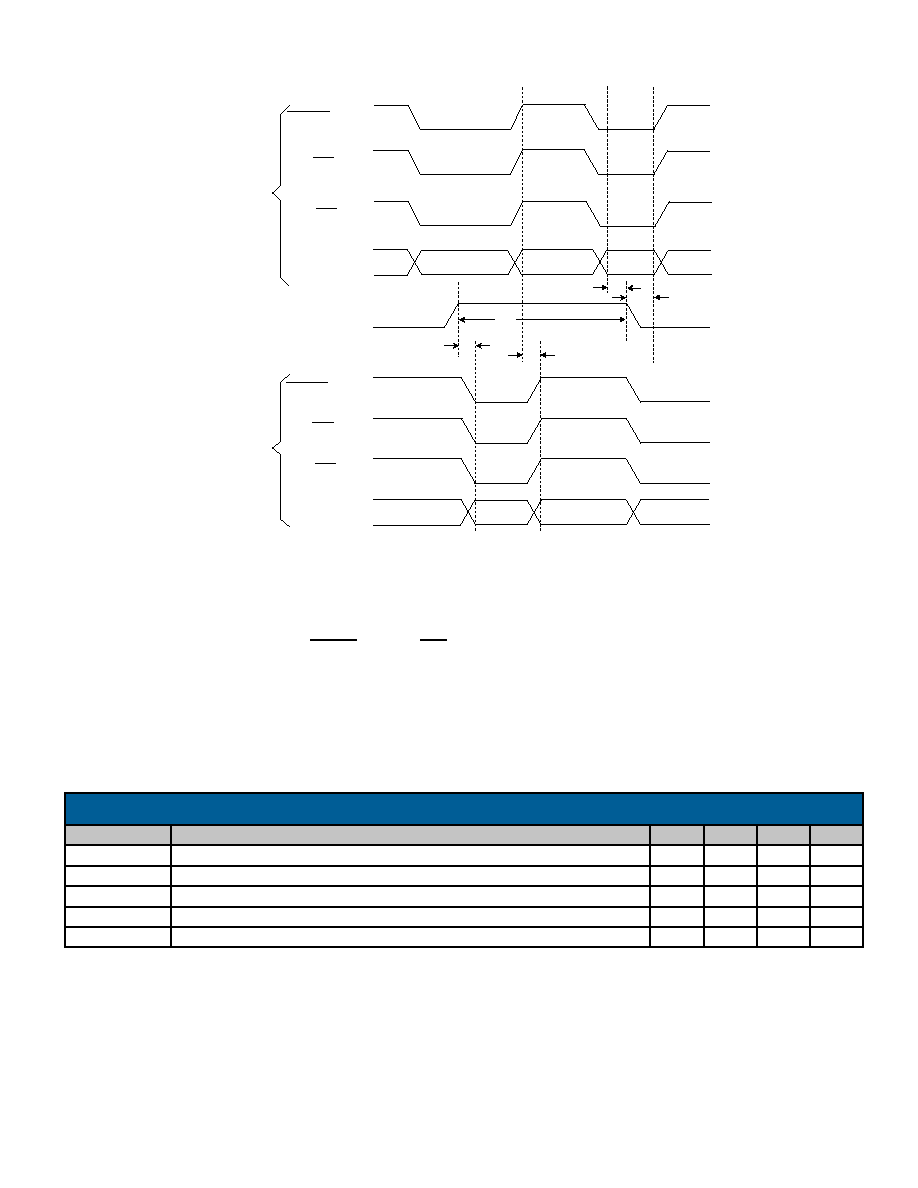

FIGURE 15. ADDRESS LATCH TIMING

Notes for FIGURE 15 and associated table.

1. Applicable to buffered mode only. Address SELECT AND MEM/REG latches are always transparent in the transparent mode of operation.

2. Latches are transparent when ADDR_LAT is high. Internal values do not update when ADDR_LAT is low.

3. MSB/LSB input signal is applicable to 8-bit mode only (16/8 input = logic “0”). MSB/LSB input is a “don’t care” for 16-bit operation.

ns

20

Input hold time following falling edge of ADDR_LAT

t5

ns

10

Input setup time prior to falling edge of ADDR_LAT

t4

ns

10

Propagation delay from external input signals to internal signals valid

t3

ns

10

ADDR_LAT high delay to internal signals valid

t2

ns

20

ADDR_LAT pulse width

t1

UNITS

MAX

TYP

MIN

DESCRIPTION

REF

TABLE FOR FIGURE 15. ADDRESS LATCH TIMING

相關(guān)PDF資料 |

PDF描述 |

|---|---|

| BU-61582D3-460W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D3-461S | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D3-591Y | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D6-101W | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

| BU-61582D6-491Q | 2 CHANNEL(S), 1M bps, MIL-STD-1553 CONTROLLER, CQIP70 |

相關(guān)代理商/技術(shù)參數(shù) |

參數(shù)描述 |

|---|---|

| BU-61585 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MIL-STD-1553 Components |ACE |

| BU-61586 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MIL-STD-1553 Components |ACE |

| BU61586V6-300 | 制造商:DDC 功能描述:MIL-STD-1553/ARINC BUS CONTROLLER/RTU, 70 Pin, Flat Pack |

| BU-61588 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MINIATURE ADVANCED COMMUNICATION ENGINE (MINI-ACE) AND MINI-ACE PLUS |

| BU-61588F0 | 制造商:未知廠家 制造商全稱(chēng):未知廠家 功能描述:MINIATURE ADVANCED COMMUNICATION ENGINE (MINI-ACE) AND MINI-ACE PLUS |

發(fā)布緊急采購(gòu),3分鐘左右您將得到回復(fù)。